Назовите признак окончания транзакции по инициативе целевого устройства повтор retry в pci

Обмен информацией по шинам PCI и PCI-X организован в виде транзакций — логически завершенных операций обмена. В каждой транзакции выполняется одна команда — как правило, чтение или запись данных по указанному адресу. Транзакция начинается с фазы адреса, в которой инициатор задает команду и целевой адрес. Далее могут следовать фазы данных, в которых одно устройство (источник данных) помещает данные на шину, а другое (приемник) их считывает. Транзакции, в которых присутствует множество фаз данных, называются пакетными. Есть и одиночные транзакции (с одной фазой данных). Транзакция может завершиться и без фаз данных, если целевое устройство (или инициатор) не готово к обмену. В шине PCI-X добавлена фаза атрибутов, в которой передается дополнительная информация о транзакции.

Состав и назначение интерфейсных сигналов шины раскрывает табл. 14.2. Состояния всех сигнальных линий воспринимаются по положительному перепаду CLK. В разные моменты времени одними и теми же сигнальными линиями управляют разные устройства шины.

Инициатор может начать следующую транзакцию и без такта покоя, такие быстрые смежные транзакции (fast back-to-back transactions) могут быть обращены как к одному, так и к разным целевым устройствам. При обмене данными в режиме PCI-X быстрые смежные транзакции недопустимы.

Каждая транзакция на шине должна быть завершена планово или прекращена по инициативе ведущего или целевого устройства.

Ведущее устройство может завершить транзакцию одним из следующих способов.

Прекращение типа retry служит для организации отложенных транзакций (delayed transactions). Отложенные транзакции используются только медленными целевыми устройствами, а также мостами PCI при трансляции транзакций на другую шину. Прекращая (для инициатора) транзакцию условием retry, целевое устройство внутренне выполняет данную транзакцию. Когда инициатор повторит эту транзакцию, у целевого устройства (или моста) уже будет готов результат (данные чтения или состояние выполнения записи), который оно быстро вернет инициатору.

Команды шины PCI

Команды PCI определяют направление и тип транзакций, а также адресное пространство, к которому они относятся. Набор команд шины PCI включает следующие:

Для каждого из трех пространств — памяти, портов ввода-вывода и конфигурационных регистров — адресация различна; в специальных циклах адрес игнорируется.

Особенности PCI-X

Протокол шины PCI-X во многом совпадает с PCI, изменения протокола нацелены на повышение эффективности использования тактов шины. В обычной шине PCI все транзакции начинаются одинаково (с фазы адреса) как пакетные с заранее неизвестной длиной. При этом реально транзакции ввода-вывода всегда имеют лишь одну фазу данных; длинные пакеты эффективны только для обращений к памяти (и применяются они именно для этого). В PCI-X транзакции по длине разделены на два типа:

В каждой транзакции после фазы адреса присутствует новая фаза передачи атрибутов транзакции, в которой инициатор сообщает свой идентификатор (номера шины, устройства и функции), тег, счетчик байтов и характеристики области памяти, к которой относится транзакция. Идентификатор инициатора вместе с тегом определяют последовательность (sequence) — одну или несколько транзакций, обеспечивающих одну логическую передачу данных, запланированную инициатором. Каждый инициатор может одновременно выполнять до 32 логических передач. Логическая передача (последовательность) может иметь длину до 4096 байт; в атрибутах каждой транзакции указывается количество байтов, которые должны быть переданы до конца данной последовательности. Общее количество байтов, передаваемых в данной транзакции, заранее не определено.

Характеристики памяти включают флаги R0 и NS:

Запросчик должен быть всегда готов к получению данных начатых им последовательностей, причем данные разных последовательностей могут приходить в произвольном порядке. Исполнитель может выдавать транзакции завершения на несколько последовательностей также в произвольном порядке.

В PCI-X 2.0 вдобавок к вышеописанным изменениям протокола появился новый режим Mode 2, отличающийся ускорением блочной записи в память и применением ЕСС-контроля. Этот режим возможен только при низком (1,5 В) напряжении питания интерфейсных схем. В данном режиме имеет место ЕСС-контроль адреса и данных (что требует дополнительных тактов). В транзакциях пакетной записи в память используется удвоенная или учетверенная скорость передачи данных по отношению к тактовой частоте (режимы PCI-X266 и PCI-X533). В Mode 2 есть возможность применения 16-битной шины (с 32-или 64-битной адресацией памяти).

Не так давно я спрашивал о механизме опроса PCI-устройств. После я устроился на работу, доделал тестовое задание, а спрашивал я именно о нем, и благополучно забыл о нем. Но недавно выдали новый проект и пришлось все вспомнить, заодно и решил написать сюда.

- Конфигурационные транзакции

- Транзакции ввода/вывода

- Транзакции обращения к памяти

- Когда ведущим устройством является южный мост

- Когда ведущим устройством является устройство, подключенное к шине PCI

И так, для работы с шиной, нам понадобятся следующие сигналы:

clk (Clock) — обеспечивает синхронизацию всех транзакций на PCI, а также является входным для каждого PCI — устройства.

AD (Address and Data) — мультиплексирования шина адреса и данных.

IDSEL (Initialization Device Select) — выбор устройства инициализации, используется для выбора кристалла при транзакциях чтения конфигурации и записи.

CBE (Bus Command and Byte Enables) — команды шины и разрешение байта.

FRAME (Frame) — сигнал выдаётся мастером в начале транзакции и определяет её длительность. Для однофазных транзакций FRAME всегда длится один такт. При многофазных транзакциях FRAME снимается за один такт до завершения транзакции.

IRDY (Initiator Ready) — сигнал готовности мастера. Он свидетельствует о готовности мастера завершить текущую фазу данных.

TRDY (Target Ready) — сигнал готовности таргета, свидетельствующий о готовности таргета завершить текущую фазу данных.

STOP (Stop) — этот сигнал выдаётся таргетом, если он хочет остановить текущую транзакцию.

PAR (Parity) — контроль четности по линиям AD и CBE.

RST(Reset) — cигнал сброса. Является асинхронным.

DEVSEL (Device Select) — сигнал выбора устройства.

Перед началом работы с любым устройством его нужно инициализировать. Поэтому рассмотрим особенности выполнения конфигурационных транзакций.

Конфигурационные транзакции. Общие сведения.

Вид на конфигурационные транзакции со стороны ОСДля генерации конфигурационных транзакций PCI на ПК используются обращения к двум портам ввода-вывода, носящим имена CONFIG_ADDRESS и CONFIG_DATA, имеющим адреса 0CF8h и 0CFCh соответственно и входящим в состав моста Host–PCI, через который шина PCI прямо или косвенно соединяется с процессором.

Порт CONFIG_ADDRESS имеет размер двойное слово и доступен только как единое целое. Обращения меньшего размера по принадлежащим ему адресам передаются на шину PCI как обычные транзакции ввода-вывода. Этот порт доступен для чтения и записи и имеет следующий формат:

Когда необходимо выполнить конфигурационную транзакцию, в этот порт записывается адрес регистра конфигурационного пространства PCI, состоящий из номеров шины (разряды 23–16), устройства (15–11), функции (10–8) и собственно регистра (7–2). Биты 1 и 0 должны всегда содержать нули, а старший бит должен содержать единицу, разрешая тем самым выполнение конфигурационной транзакции. Разряды 30–24 зарезервированы и должны содержать нули.

Собственно генерация конфигурационной транзакции происходит при чтении или записи порта CONFIG_DATA, когда в CONFIG_ADDRESS был записан адрес с установленным старшим битом и номером шины, соответствующим шине, подключенной к мосту Host–PCI, или любой шине PCI, лежащей ниже этой шины и соединённой с ней через один или несколько мостов PCI–PCI (допустимый диапазон номеров шин задаётся мосту Host–PCI в процессе его настройки). Доступ к порту CONFIG_DATA должен иметь размер, равный размеру считываемого или записываемого конфигурационного регистра, адрес которого находится в CONFIG_ADDRESS.

Если номер шины, заданный в CONFIG_ADDRESS, совпадает с номером шины, подключённой непосредственно к мосту Host–PCI, генерируется конфигурационная транзакция с адресом типа 0, причём номер устройства, находящийхся в разрядах 15–11 порта CONFIG_ADDRESS, используется для выдачи одного из сигналов IDSEL, которые и служат для выбора конкретного устройства. Кроме того, декодированный номер устройства (один единичный и остальные нулевые биты) в фазе адреса конфигурационной транзакции передаётся в разрядах 31–11 адреса.

Если адрес в CONFIG_ADDRESS указывает не ту шину, которая непосредственно подключена к мосту Host–PCI, последний генерирует конфигурационную транзакцию с адресом типа 1. Она будет обработана мостом PCI–PCI, который опознает содержащийся в адресе номер шины. Этот мост либо выполнит конфигурационную транзакцию с адресом типа 0 (если адресуемое устройство подключено к шине, прямо подсоединённой к этому мосту), либо сгенерирует транзакцию с адресом типа 1, обеспечив тем самым её прохождение через следующий мост. Длина этой цепочки теоретически ограничена только разрядностью поля, отведённого под номер шины (8 бит).

Если при выполнении транзакции выяснится, что адресуемого конфигурационного регистра не существует (указан номер несуществующей шины, устройства, функции или регистра), то операция записи не возымеет никаких действий, а операция чтения вернёт процессору значение, содержащее единицы в каждом разряде

Формат адреса для транзакции типа 1.

Формат адреса для транзакции типа 0.

- Vendor ID — поле идентифицирует изготовителя устройства. Запрещено использовать значение 0xFFFF.

- Device ID — поле идентифицирует конкретный вид устройства. Запрещено использовать значение 0xFFFF.

- Revision ID — дополнение к идентификатору устройства. Может быть равно нулю.

- Header Type — Для многофункциональных устройств. Если 7ой бит равен 0, то устройство является однофункциональным, иначе — многофункциональное.

- Class Code — доступен только для чтения. Используется для идентификации общего функционального назначения устройства. Старший байт (адрес 0Bh) определяет базовый класс, средний — подкласс, младший — программный интерфейс (если он стандартизован).

- Subsystem ID, Subsystem Vendor ID — задаются производителем. Только для чтения. Хранят идентификаторы, позволяющие точно идентифицировать карты и устройства (в системе могут быть установлены

несколько карт с совпадающими идентификаторами устройства и производителя (Device ID и Vendor ID). - BAR0 — BAR5 — описывают области памяти и портов ввода-вывода.

- Бит 0 = 0 — признак памяти. Размером не более 2 Гбайт

- Бит 0 = 1 — признак области портов. Размером до 256 байт.

Общий алгоритм выполнения транзакций

Мастер выставляет на шине AD адрес устройства, на шине CBE выполняемую команду, устанавливает сигнал FRAME в 0 и сигнал IRDY в 0. Далее, мастер ждет от таргета — выставления им сигналов TRDY и DEVSEL. Так же, таргет выставляет на шину AD запрашиваемые данные. Данные считаются валидными, когда IRDY, TRDY и DEVSEL равны уровню логического нуля.

Реализация

Для обращения к выводам ПЛИС потребуются специальные компоненты: буферы ввода/вывода для работы с Z — состоянием.

Так, для шины AD подключение будет выглядеть следующим образом:

- O — выход буфера.

- IO — вход/выход буфера, непосредственно подключается к выводу ПЛИС.

- I — выход буфера.

- T — управление входом, уровень единицы — вход, уровень нуля — выход.

Как я уже писал выше, при начале транзакции, когда на шине AD выставлен адрес, всегда сигнал FRAME равен нулю. Ниже приведен код, который формирует сигнал AdrPhASE, во время действия которого нужно защелкнуть шину адреса и шину команд для последующей работы. Фактически сигнал AdrPhASE есть ни что иное, как выделение спадающего фронта сигнала FRAME, что однозначно идентифицирует начало транзакции.

Далее, работу всего устройства можно описать с помощью автомата.

- 0010 I/O Read

- 0011 I/O Write

- 0110 Memory Read

- 0111 Memory Write

- 1010 Configuration Read

- 1011 Configuration Write

Чтение конфигурации

Как было описано выше, для обработки устройством используются транзакции типа 0. Так как устройство однофункциональное, то номер функции — 000, который проверятся в управляющем автомате. В зависимости от номера регистра (биты 7..0 шины AD) на шину AD выдается нужный регистра, согласно рисунку выше.

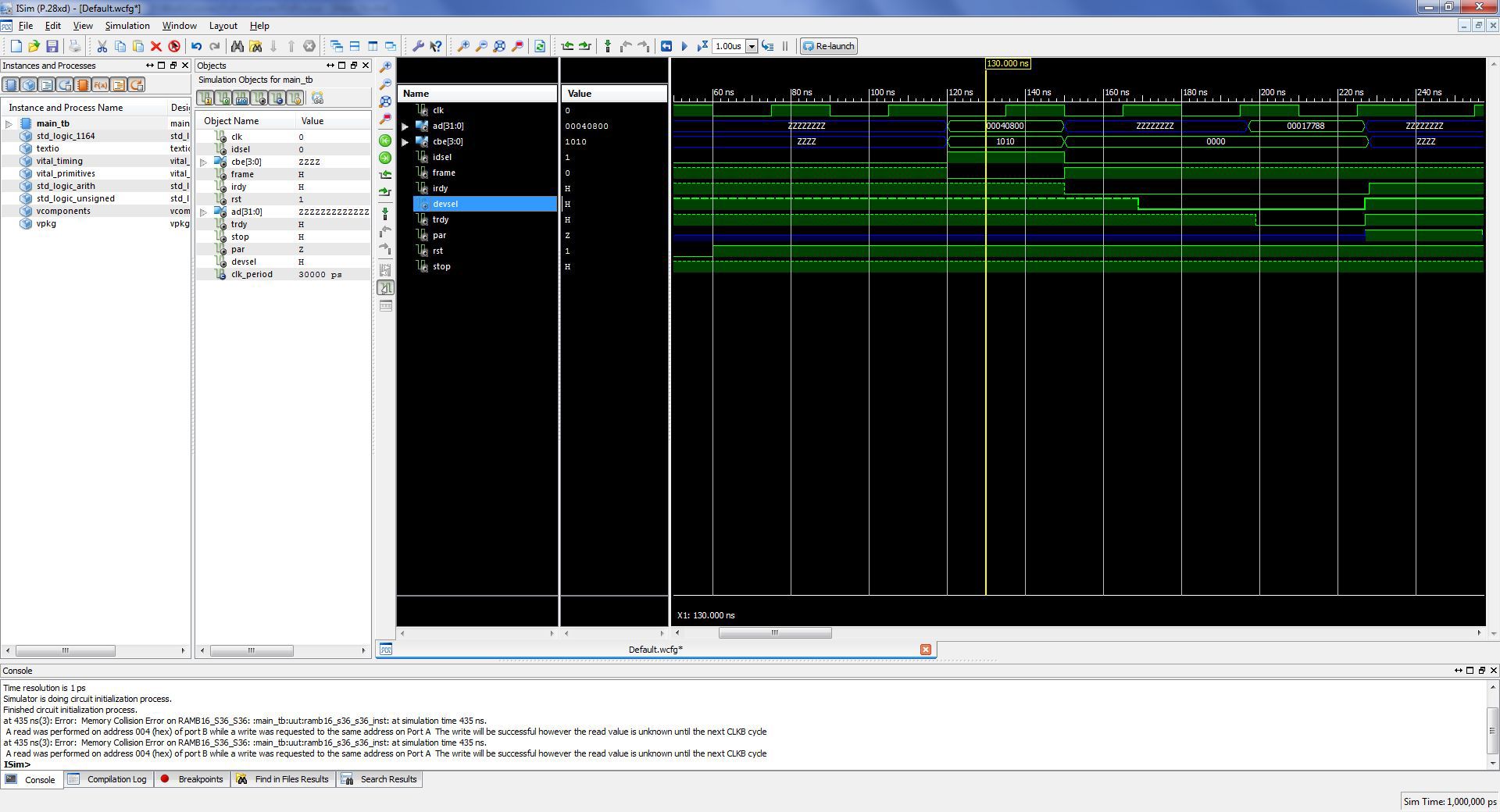

Так выглядит чтение конфигурации в симуляторе:

Запись конфигурации

На шине AD мастер выставляет адрес регистра для записи, а в следующем такте выставляются данные, которые нужно записать. В BAR0 биты 7..0 являются read-only, в BAR1 биты 15..0 являются read-only. Поэтому адресов ввода/вывода 256, адресов памяти 4 294 967 296.

Запись в порт

На шине AD мастером выставляется номер регистра для записи, в следующем такте выставляются данные, которые нужно записать.

Приведем пример только для записи одного регистра, остальные записываются аналогично.

Чтение порта

На шине AD мастером выставляется номер регистра, который нужно прочитать. Затем устройство выдает на шину AD запрашиваемые данные.

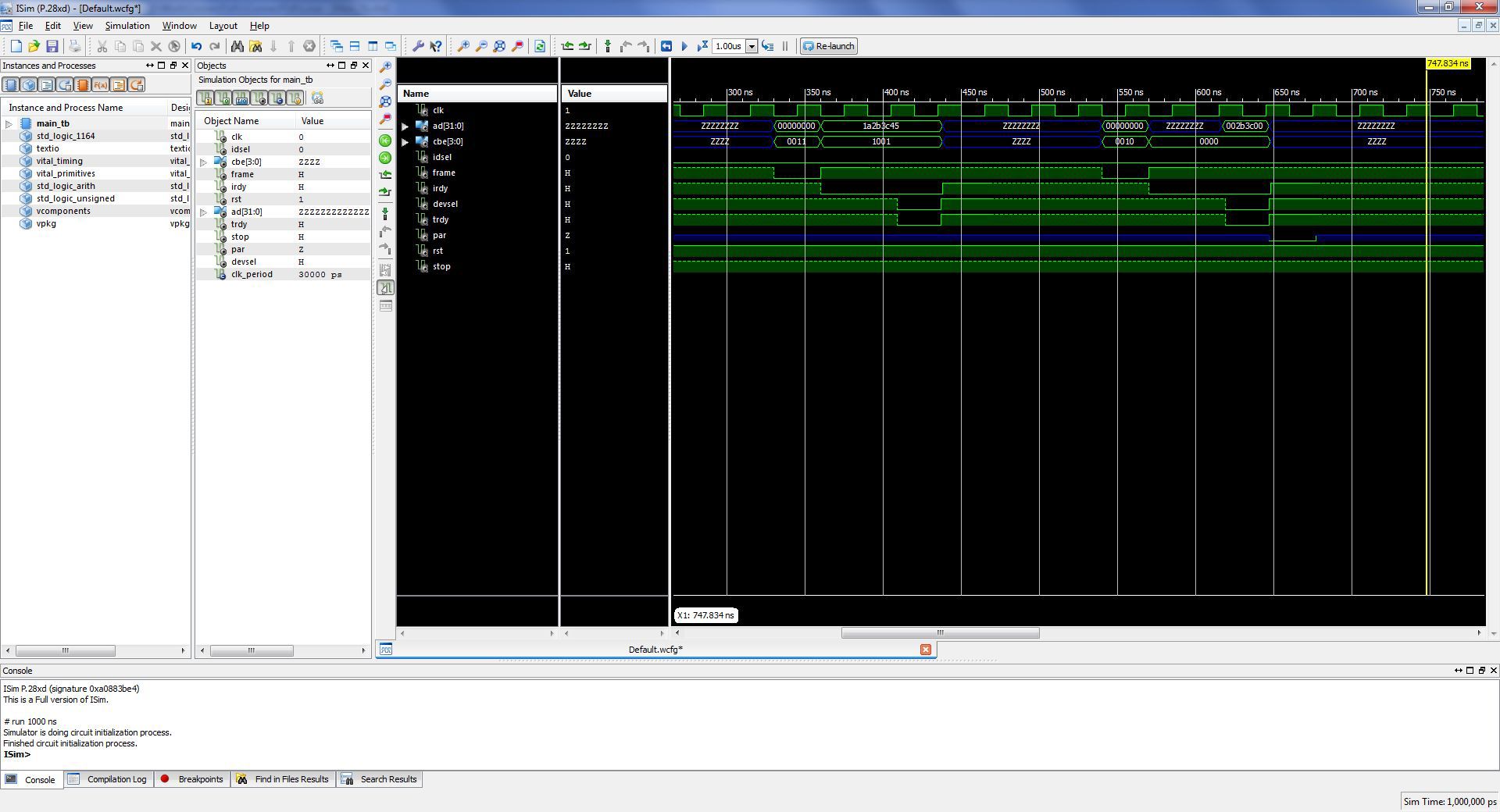

Так выглядит запись и чтение порта ввода-вывода:

Запись и чтение памяти

На шине AD мастер выставляется адрес, по которому нужно записать данные, а в следующем такте сами данные. При чтении на шину AD мастер выставляет адрес для чтения, затем на шину AD таргет выставляет сами данные.

Данные пишутся в RAM в порт А, читаются из порта B.

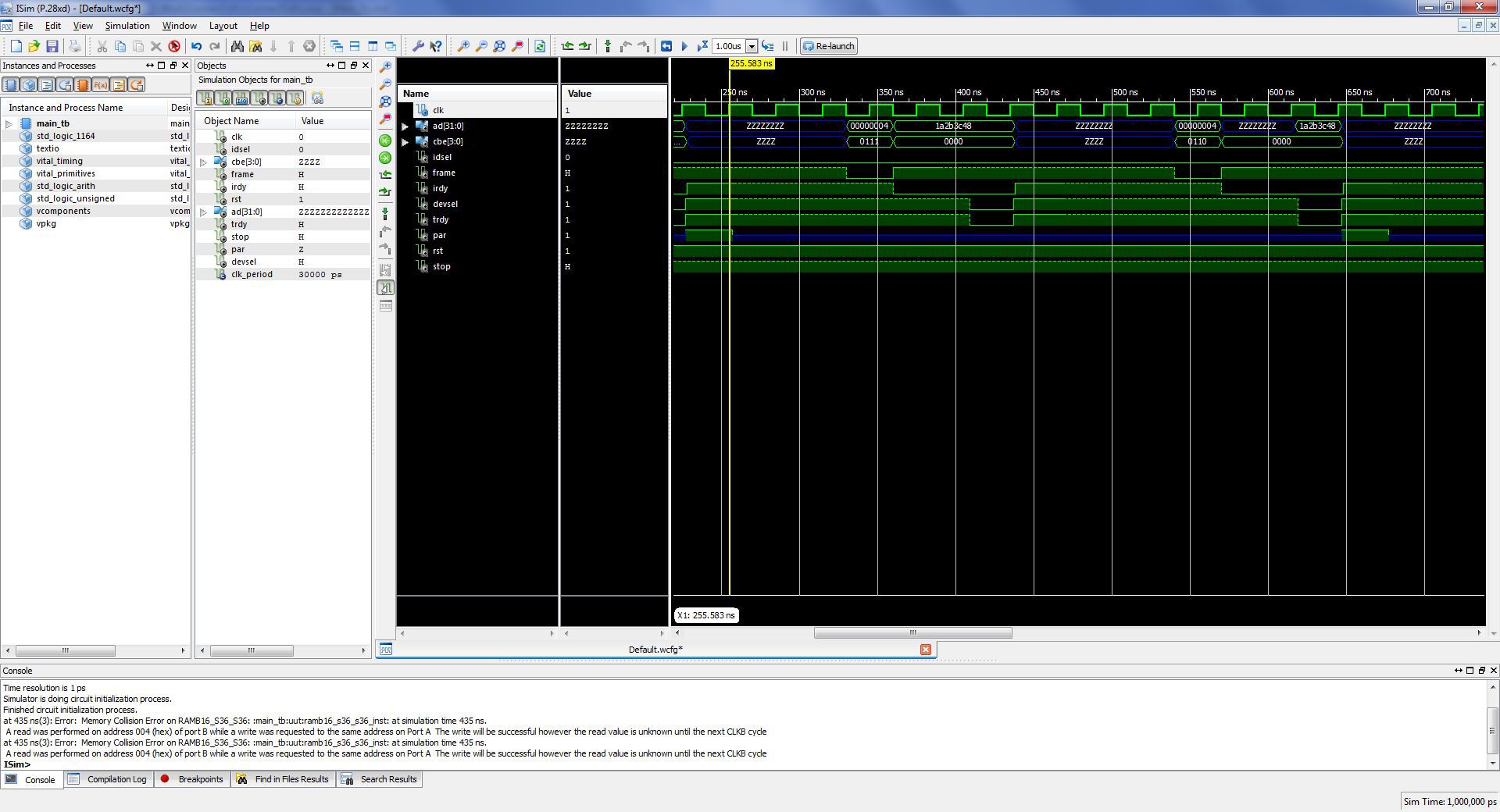

Так выглядит запись и чтение памяти в симуляторе:

Данные на шину AD выводятся следующим образом. В зависимости от состояния автомата, к выходному буферу подключается соответствующий регистр.

Сигнал разрешения выдачи данных на шину AD формируется следующим образом:

Отдельно хотелось бы добавить про компонент STS на примере выработки сигнала DEVSEL

Так как, активные уровни управляющих сигналов равны нулю, то для перехода в Z — состояние и отпускания линии нужно предварительно выдать уровень логической единицы и только потом перевести в Z — состояние.

Заключение

В заключение хочу сказать, что выполнение транзакций на шине PCI не так сложно как кажется. Разработанная прошивка была залита в ПЛИС. Плата с ПЛИС вставлена в PCI слот и был включен компьютер. Система нашла плату и запросила драйвера на нее.

Работает! :)

Обмен информацией по шинам PCI и PCI-X организован в виде транзакций— логически завершенных операций обмена.

В каждой транзакции выполняется одна команда— как правило, чтение или запись данных по указанному адресу. Транзакция начинается с фазы адреса, в которой инициатор задает команду и целевой адрес. Далее могут следовать фазы данных, в которых одно устройство (источник данных) помещает данные на шину, а другое (приемник) их считывает. Транзакции, в которых присутствует множество фаз данных, называются пакетными. Есть и одиночные транзакции (с одной фазой данных). Транзакция может завершиться и без фаз данных, если целевое устройство (или инициатор) не готово к обмену. В шине PCI-X добавлена фаза атрибутов, в которой передается дополнительная информация о транзакции.

Любое устройство шины может выступать как в роли инициатора транзакций (задатчика), так и в роли целевого устройства. Целевое устройство отвечает на транзакции, адресованные к его ресурсам (областям памяти и портам ввода-вывода).

Каждая физическая шина PCI позволяет объединять лишь небольшое число устройств (обычно не более шести). Для увеличения числа подключаемых устройств применяют мосты PCI (PCI-to-PCI Bridge) — специальные аппаратные средства с парой интерфейсов, которыми шины объединяются в древовидную структуру. В корне этой структуры находится хост — «хозяин шины», в обязанности которого входит конфигурирование всех устройств, включая мосты. В роли хоста, как правило, выступает центральный процессор с главным мостом.

Важной частью шины PCI является система автоматического конфигурирова ния: конфигурирование выполняется каждый раз при включении питания и инициализации системы. Специальное конфигурационное программное обеспечение позволяет обнаружить и идентифицировать все установленные устройства, а также выяснить их потребности в ресурсах (областях памяти, адресах ввода - вывода, прерываниях).

Основные сигналы шины PCI, котрые используются в транзакциях:

AD - Address / Data - мультиплексированная шина адреса/данных. В начале транзакции передается адрес, в последующих тактах – данные;

С/ВЕ - Command / Byte Enable — команда/разрешение обращения к байтам. Команда, определяющая тип очередного цикла шины, задается четырехбитным кодом в фазе адреса;

FRAME - Кадр. Введением этого сигнала отмечается начало транзакции (фаза адреса), снятие сигнала указывает на то, что последующий цикл передачи данных является последним в транзакции;

DEVSEL - Device Select - устройство выбрано (ответ целевого устройства (ЦУ) на адресованную к нему транзакцию);

IRDY - Initiator Ready — готовность ведущего устройства к обмену данными;

TRDY - Target Ready — готовность целевого устройства к обмену данными.

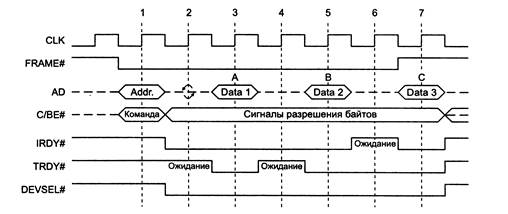

Рис. 5.25 Цикл обмена на шине PCI.

Для адреса и данных используются общие мультиплексированные линии AD. Линии С/ВЕ[3:0] обеспечивают кодирование команд в фазе адреса и разрешение байтов в фазе данных.

В начале транзакции ведущее устройство активирует сигнал FRAME, передает целевой адрес по шине AD, а по линиям С/ВЕ - информацию о типе транзакции (команду).

Адресованное целевое устройство отзывается сигналом DEVSEL. Ведущее устройство указывает на свою готовность к обмену данными сигналом IRDY.

Когда и целевое устройство оказывается готово к обмену данными, оно устанавливает сигнал TRDY. Данные по шине AD передаются только при одновременном наличии сигналов IRDY и TRDY. С помощью этих сигналов ведущее, и целевое устройства согласуют свои скорости, вводя такты ожидания (wait states).

На рис. 5.25 приведена временная диаграмма обмена, в которой и ведущее и целевое устройства вводят такты ожидания. Если бы они оба ввели сигналы готовности в конце фазы адреса и не снимали бы их до конца обмена, то в каждом такте после фазы адреса передавалось бы по 32 бита данных, что обеспечило бы выход на предельную производительность обмена.

С увеличение производительности вычислительной техники шина PCI перестала удовлетворять требованиям по скорости и пропускной способности. Программисты создавали все более красочные игрушки, а для передачи красивой картинки нужна высокая пропускная способности. Поэтому постепенно видеокарты стали подключаться через порт AGP.

Шина PCI - Express .

PCI - Express - новая архитектура соединения компонентов, известная и под названием 3 GIO (3-Generation Input/Output — ввод-вывод 3-го поколения). Дата появления этой шины – 22 июля 2002 года, когда была опубликована базовая спецификация шины и требования к энергопотреблению. Сфера применения шины PCI-Express — от соединений между микросхемами на плате до межплатных разъемных и кабельных соединений, применяется в компьютерах разных классов, телекоммуникационных устройствах и встроенных системах.

Фактически шина PCI-Express представляет собой совокупность независимых самостоятельных последовательных каналов передачи данных. Сигнальный уровень составляет 0,8В. Каждый канал состоит из двух дифференциальных сигнальных пар.

В архитектуре PCI-Express сохраняются многие программные черты шины PCI, что обеспечивает плавный переход от PCI к PCI Express. Однако, появились новые возможности: управление качеством обслуживания (Quality of Service), потреблением и бюджетом связей. Протокол PCI Express характерен малыми накладными расходами и малыми задержками выполнения транзакций.

Механическое удерживание земляных масс: Механическое удерживание земляных масс на склоне обеспечивают контрфорсными сооружениями различных конструкций.

Опора деревянной одностоечной и способы укрепление угловых опор: Опоры ВЛ - конструкции, предназначенные для поддерживания проводов на необходимой высоте над землей, водой.

Поперечные профили набережных и береговой полосы: На городских территориях берегоукрепление проектируют с учетом технических и экономических требований, но особое значение придают эстетическим.

Организация стока поверхностных вод: Наибольшее количество влаги на земном шаре испаряется с поверхности морей и океанов (88‰).

Отложенные транзакции выполняются мостом PCI для всех транзакций обращения к устройствам ввода-вывода и конфигурационным регистрам, а также всех разновидностей транзакций чтения памяти.

Отложенные транзакции выполняются в три фазы:

- запрос транзакции устройством-инициатором (обмена данными с целевым устройством еще нет);

- завершение транзакции целевым устройством(мостом);

- завершение транзакции устройством-инициатором.

Вопрос 11

Интерфейс PCI имеет две особенности с точки зрения электрических характеристик, которые определяют подход к выбору схемотехнических решений приемо-передатчиков:

- магистраль интерфейса PCI это магистраль КМДП – типа.

- в линиях связи интерфейса PCI принципиально используются отражения в линиях связи при формировании сигнала.

Формирование нарастающего фронта сигнала в линии связи

Uпад = Uл (0,5Zо/(0,5Zо+0,5Zо))=Uл/2

распространяется по обоим участкам линии и, достигнув конечных точек, вызывает отраженные волны Uотр=КотрUпад=Uпад,

где Котр=(Rн-Zо)/(Rн+Zо)=1, т.к. Rн>>Zо.

Результирующее (суммарное) напряжение Uа и Uс в точках А и С в этот момент (t=0,12нС) становиться равным Uл, рис.2.1.18с. В момент t=0,24нС, отраженные от концов линии B и С волны амплитудой напряжения Uл/2, возвращаются к середине линии связи (точка А). Каждая из этих волн в свою очередь порождает новую отраженную волну напряжения амплитудой

где Rн.экв= (Z о×Zо/2)/(Zо+Zо/2)=Zо/3

и проходит как падающая волна напряжения на противоположный участок линии связи того же знака амплитудой Uл/4, поскольку проходящая волна равна алгебраической сумме падающей и отраженной волн в точке Вв момент t=0,24нС Суммарная падающая волна, приходящая в момент времени t=0,36 нС в точку А и в точку С равна 0. Отражения в линии заканчиваются и приближенно (предположение о нулевых временах нарастания сигнала) можно считать, что напряжения на концах линии устанавливаются через 0,24 нС и составляют величину Uл.

Плата расширения PCI и расположение ключей на ней

Вопрос 12

Системный интерфейс CompactPCI предназначен для создания компьютерных систем:

- реального времени, использующихся в промышленной автоматизации,

- сбора и обработки данных, в тренажёрах и стендовом оборудовании,

- специального (военного) применения и т.п.

Интерфейс CompactPCI используется в основном, там, где требуется:

- оптимальные возможности для работы современных микропроцессоровPentium, PentiumMMX, PentiumPRO, Pentium II, PowerPC, ALPHA, UltraSPARC и перспективных микропроцессоров;

- модульность построения системы;

- надёжность;

- устойчивость к воздействию жестких климатических, механических и радиационных факторов (температурных воздействий, вибрации, пыли, электромагнитных помех и т.д.);

- уменьшенные вес и габариты;

- простота модернизации и удобство обслуживания;

- малое время восстановления системы и улучшенные характеристики ремонтопригодности;

- возможность замены модуля без выключения питания ("горячей замены").

Интерфейс CompactPCI является 100% электрическим и логическим аналогом интерфейса PCI и поэтому обеспечивается полное использование всего огромного парка недорогих PCI интегральных схем.

В отличие от обычных PCI модулей для настольных офисных компьютеров, в CompactPCI-модулях в качестве соединителей (разъемов) используются высоконадежные пятирядные 235- штырьковые соединители (раъемы) с шагом контактов 2мм, соответствующие стандартам МЭК (в частности МЭК1076-4-101).

Стандарт CompactPCI, по сравнению со стандартом PCI для настольных персональных компьютеров, имеет, по крайней мере, два важнейших преимущества:

- удвоенное количество подключаемых модулей к пассивной кросс - плате: 8 против 4;

- значительно более приспособленную для промышленных условий эксплуатации механическую конструкцию, в частности, конструкция модулей обеспечивает проверенную годами успешной эксплуатации схему крепления в четырех точках CompactPCI- модуля и совершенную, столь необходимую для современной КМОП - микроэлектроники, защиту от электростатических разрядовпри установке модулей в еврокрейт (блок);

- используемые в CompactPCI- модулях промышленные разъемы штыревого типа значительно более надежны, имеют лучшие характеристики по устойчивости к ударам, вибрации, пыле и защите от влаги, чем печатные разъёмы, применяемые для PCI-модулей обычных настольных персональных компьютеров. Сигнальные и питающие контакты CompactPCI- разъема конструктивно выполнены так, что возможна установка и замена модуля без выключения питания крейта (блока), что чрезвычайно важно в системах повышенной надежности.

Читайте также: