Триггер как элемент памяти компьютера

Базовым элементом памяти является триггер . Устройство, предназначенное для хранения одного бита информации.

Для более полного понимания вопроса рекомендуется посмотреть статью про элементы памяти . Если без подробностей, то у базового элемента памяти три рабочих режима. Хранение , установка и сброс . Возможность запоминания бита информации приходит при дополнении этой схемы несколькими элементами.

D-триггер это такая же ячейка памяти, но с дополнительной логикой. Она позволяет при высоком уровне сигнала C запоминать состояние линии D . При этом если D нулевая, то триггер сбрасывается, а если D единица, то триггер устанавливается. Таким образом, происходит как бы запоминание сигнала на входе. Единственный недостаток такой схемы это именно срабатывание по высокому уровню тактирующего сигнала.

Промышленные триггеры работают по фронту или спаду тактирующего сигнала.

Если собрать триггер из двух одинаковых половинок, то можно обеспечить тактирование по фронту.

При низком уровне тактового сигнала содержимое D записывается в зеленую половину, но как только низкий уровень тактирующего сигнала сменяется на высокий, содержимое зеленой половины записывается в красную. Состояние линии D записывается в триггер только по переднему фронту тактового сигнала. При этом записанный бит появляется на выходе Q .

Описание элемента памяти на языке Verilog

В языке Verilog для описания триггеров предусмотрена довольно простая конструкция. Это процедурный блок, где в списке чувствительности значится передний фронт тактового сигнала. Для переднего фронта предназначено слово posedge , для заднего фронта negedge .

Внутри процедурного блока присвоение выходу входного сигнала. Если бы в списке чувствительности не значился тактовый сигнал, то такое описание означало бы просто провод. Но тактовый сигнал означает действие только по переднему фронту. Все время между фронтами состояние выхода запоминается и запоминает его D-триггер .

Как мы помним , в состав логической ячейки ПЛИС кроме LUT таблицы входит еще элемент памяти. Это D-триггер с разрешением и асинхронным сбросом. Опишем такой элемент при помощи языка Verilog. Для того чтобы сбрасывать состояние триггера не зависимо от тактового сигнала, необходимо в списке чувствительности указать еще один сигнал, по фронту которого произойдет некоторое событие.

Описание D-триггера с асинхронным сбросом и разрешением Описание D-триггера с асинхронным сбросом и разрешениемНам нужен сброс. Внутри процедурного блока опишем действие, происходящее по высокому уровню сигнала сброса. На выход модуля отправляется ноль. Иначе если сброса нет, то будет происходить другая работа. В случае сигнала разрешения происходит запоминание входного сигнала. Соответственно, если разрешения не будет , то и запоминание не произойдет.

Промоделируем этот триггер. Для этого разработаем модуль теста.

Количество проводов соответствует количеству входов и выходов триггера. Вписываем триггер в состав теста. Соединяем его входы и выходы с проводами. Каждые 50 пикосекунд состояние тактовой линии будет меняться на противоположное. Чтобы это все заработало, нужно задать начальное состояние тактовой линии и сделать это можно в секции initial begin . В начальный момент времени среди всех входных сигналов и у тактовой линии есть какое-то состояние. Посмотрим результат моделирования.

Тактовый сигнал ( clk ) подается непрерывно. В какой-то момент времени сигнал сброса ( aclr ) привел триггер в состояние нуля из состояния неопределенности. Неопределенность это либо ноль либо единица. Это неизвестно, потому как начальное состояние триггера нигде не было указано. Поступление единицы на вход D ни к чему не приводит, потому, что сигнал разрешения нулевой.

Потом в тесте разрешим работу триггера ( en=1 ) и отправим на некоторое время единицу на вход D . Как раз, в момент прихода переднего фронта тактового сигнала бит единица записался в триггер и оказался на его выходе. Как только состояние входного бита изменилось, то запись не произошла сразу, для записи опять же необходим передний фронт тактового сигнала. На этом этапе нужно особенно внимательно подойти к пониманию этих процессов, иначе потом будет непросто.

Использование элементов памяти в модулях поведенческого стиля описания

Теперь посмотрим как ненавязчиво создавать элементы памяти и не перегружать схемы структурным стилем описания. При структурном стиле мы вынуждены описывать экземпляры триггеров и соединять их проводами. Но все можно делать более незаметно. Ниже описание триггера и конъюнкции, причем запоминание результата происходит по переднему фронту тактового сигнала.

Элемент памяти, называемый триггером представляет собой довольно интересную конструкцию.

Устройство триггера (RS-триггер)

В одном из вариантов это две функции Стрелка Пирса, соединенные между собой через обратные связи. Это то, что придает привычным вещам весьма необычные свойства. Триггер при воздействии нулей на его входы R и S может находиться в одном из двух стабильных состояний. Это состояние ноль на выходе Q и состояние один на выходе Q. Выход Q определяет состояние триггера. При этом на выходе не Q наблюдается сигнал, противоположный Q.

Стабильные состояния триггера

Действительно, если рассмотреть схему вместе с таблицами истинности, то по всей цепочке распространения сигнала мы не увидим никаких противоречий.

Вентиль стрелка Пирса

Пошагово рассмотрим все режимы работы триггера.

Режим хранения

Начальное его состояние обозначим в таблице как Q прошлое. Как мы помним, состояний может быть два. Назовем любую единицу на входе триггера воздействием на него. Ноль это отсутствие воздействия. Для начала убираем всякое воздействие на триггер и видим, что состояние триггера не меняется.

Режим хранения триггера

Это полезный режим работы. Называется он — режим хранения.

Режим установки

Дальше воздействуем на триггер через вход установки. В этом случае состояние триггера установится в единицу какое бы состояние не было начальным. Этот полезный режим называется установкой.

Режим установки триггера

Режим сброса

Теперь воздействуем на элемент памяти через вход Reset. Как можно заметить, из любого прошлого состояния триггер переходит в нулевое состояние и этот полезный режим работы называется режим сброса.

Режим сброса триггера

Запрещенное состояние

Ради интереса выставим на входы все единицы одновременно. В большинстве учебников это состояние называется запрещенным, хотя ничего запрещенного в нем нет.

Так называемое, запрещенное состояние триггера

Просто в этом режиме нет никакой пользы. Рассмотренный триггер называется RS триггером по названию входных линий. Он является простым элементом памяти и служит основой для чуть более сложного.

D триггер

Немного улучшений в RS триггер придадут ему еще больше полезности. Для начала снабдим его управляющим входом C. Как можно заметить, этот вход через коньюнкцию отрывает ячейку памяти от внешних воздействий. Таким образом, без единицы на входе C триггер будет продолжать хранить информацию что бы ни происходило на входах. Такой триггер назовем синхронным RS триггером. Дальше оставим один вход D. Причем инвертируем его для подачи в то место где был сброс, оставим без изменения для подачи в то место, где была установка.

Модификация RS триггера до D триггера

Вот тут произойдет самое интересное. Теперь мы имеем возможность сохранять состояние сигнала D, это произойдет при подаче единицы на вход C. Действительно, если D было равно единице, то произойдет установка триггера. Если на D ноль, то произойдет сброс. Такой триггер называется D триггером.

Настоящий D триггер, используемый в цифровой схемотехнике работает не просто с высоким уровнем входа C, а в момент смены состояния уровня синхронного входа. В этом случае достигается максимальная синхронность., ведь сам момент смены это высокоскоростной физический процесс, который происходит за миллиардные доли секунды, учитывая все современные достижения науки и техники.

Устройство D триггера

Как можно заметить, D триггер теперь состоит из двух, но управляющий вход C в один из них приходит с инверсией, в другой в неизменном состоянии. Это позволяет при нулевом уровне C записать один бит в зеленую половину, но как только состояние C сменится на единицу, то содержимое зеленой половины запишется в красную. Такую работу называют работой триггера по переднему фронту тактирующего сигнала. Если инвертор перенести в красную часть, то триггер станет работать по заднему фронту тактирующего сигнала.

Параллельный регистр

В завершении нашего обзора стоит упомянуть, что соединять D триггеры можно как параллельно, так и последовательно. Если необходимо хранить не один бит, а двоичные коды из множества бит, то применяют параллельное соединение. Его называют регистром.

У косой черты обычно указывают сколько бит может хранить такая схема.

Сдвиговый регистр

Очень часто необходимо организовать последовательное движение бит один за одним. В этих задачах применяются последовательные соединения D триггеров.

Теперь у такой схемы на входе не двоичное слово, а один бит, но на выходе можно считать несколько хранящихся там бит одновременно. Обычно число таких бит написано около косой черты. Самое яркое применение такой конструкции это простая бегущая строка.

Поддержите статью репостом если понравилось и подпишитесь чтобы ничего не пропускать, а также посетите канал на YouTube c интересными материалами в формате видео.

То, что компьютеры могут хранить информацию в памяти, мы давно принимаем за данность, но знаешь ли ты, как именно эта память работает? В этой статье мы поговорим о последовательностной логике, которая позволяет компьютерам хранить информацию. Какие возможности это открывает и реально ли узнать секретный ключ кодового замка, располагая только его схемой — самое время это выяснить!

В начале был Бит

Пару месяцев назад мы приступили к изучению цифровой схемотехники с базового блока NOT . Не будем изменять традиции и в этот раз, тем более, что блок на самом деле не так прост, как кажется на первый взгляд. Возьмем парочку и соединим их последовательно.

Кто-то может сказать, что это совершенно бессмысленная схема, ведь сигнал на выходе всегда равен входу. Действительно, применяя логическое отрицание дважды, мы получаем исходное утверждение. Если ты не «белый» хакер, ты «черный». Не «не белый» — по-прежнему «белый». Это выглядит как бесполезная словесная эквилибристика, но все меняется, если в схеме выше попробовать вход замкнуть на выход.

Теперь, если в правой половине у нас высокий логический уровень, в левой половине всегда будет низкий (и наоборот). Иначе говоря, схема приобретает свойство бистабильности и принимает лишь одно из двух возможных состояний. Совсем как бит памяти — или переменная bool в С/С++.

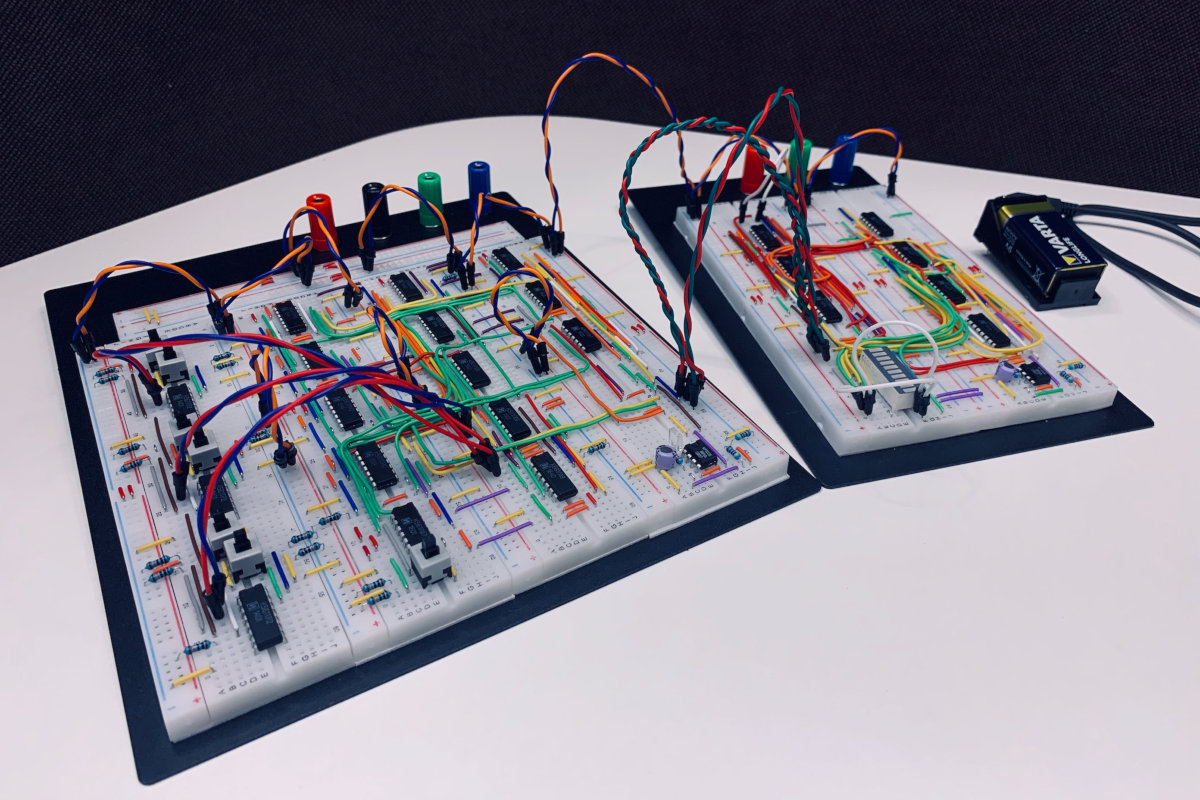

Для наглядности можно собрать схему на макетной плате. Здесь подойдет любой интвертор — например, 74HC04B. Это шесть логических вентилей NOT в корпусе DIP-14 (целых три бита информации, Карл!). Впрочем, как ты уже понимаешь, одну и ту же функцию можно реализовать несколькими способами, поэтому здесь наш выбор практически неограничен.

Тут стоит упомянуть, что с теми же целями мы можем использовать и 74HC00N (четыре элемента NAND ). Эта микросхема получила свой особый «нулевой» номер в серии 74хх не просто так — логическая операция ИЛИ-НЕ обладает замечательным свойством функциональной полноты. Иными словами, мы можем любой другой базовый блок ( AND , OR и остальные) разложить на комбинацию блоков NAND . Аналог в отечественной микроэлектронике — 155ЛА3 и это настолько популярная микросхема у радиолюбителей, что в ее честь даже называют сайты.

Простой пример (как на картинке выше) позволяет на практике убедиться, что микросхема работает, как мы предполагали. Для мигания светодиодами и переключения состояний в такой ячейке памяти достаточно прикасаться концами проводов (от земли или питания) к соответствующим выводам микросхемы. Возможно, само по себе это звучит и не очень увлекательно, но некоторое размышление в процессе должно навести на интересные идеи.

Некоторая неопределенность

В какой-то момент твой пытливый хакерский ум наверняка задался вопросом — а что если подать одно и то же напряжение на обе половинки одновременно? И в каком состоянии окажется наша схема после? В сущности, это сродни делению на ноль в математике (или программировании) — запрещенная операция, результат на выходе которой не определен. Парадоксально, но даже такое свойство может иметь практическое применение! Инженеры в Intel хорошо знают схемотехнику (кто бы сомневался) и встроенный в их процессоры генератор случайных чисел работает именно по такому принципу.

Сейчас процесс работы нашей схемы напоминает электромеханические компьютеры середины 40-х годов XX века, когда коммутация сигналов внутри устройства происходила с помощью реле и переключателей. Самое время добавить новые возможности и перейти от инверторов к элементам с несколькими входами.

Простой RS-триггер

Внесем минимальные изменения в нашу схему и воспользуемся дополнительными входами NAND . Назовем их nR и nS ( not RESET и not SET соответственно, их назначение прояснится в дальнейшем).

Оба входа могут принимать по два значения, итого предстоит разобрать четыре варианта. Начнем с базового случая nR = 1 и nS = 1 . При этом на выходах Q и nQ уже есть какие-то значения. Обрати внимание, что если Q = 1 , то при nS = 1 результатом операции NAND будет низкий уровень, то есть nQ = 0 . И наоборот, если Q = 0 , то nQ = 1 и оба выхода в нашей схеме действительно принимают противоположные значения. Другими словами, если один из входов вентиля NAND находится в состоянии логической единицы, то сигнал на выходе определяется как инверсия второго входа — в точности как с инверторами чуть ранее! Таким образом, при nR = 1 и nS = 1 схема сохраняет свое старое состояние и выходы не обновляются.

Теперь рассмотрим вариант с nR = 1 и nS = 0 . Так как на входе верхнего элемента NAND точно есть хотя бы один ноль, то его выход в любом случае будет равен логической единице. Значит, Q = 1 и, следовательно, nQ = 0 . Аналогично, при nR = 0 и nS = 1 мы можем схожим образом вывести, что состояние схемы будет полностью противоположным ( Q = 0 и nQ = 1 ).

Остается разобрать заключительный вариант, где оба входа равны нулю одновременно. На интуитивном уровне можно уже предполагать, что тут что-то не так. Действительно, при nR = nS = 0 результат элемента NAND не может быть положительным ни при каких возможных значениях дополнительного входа (рекомендую проверить по таблице истинности). Следовательно, Q = nQ = 0 и это единственный случай, когда наша схема «сбоит». В дальнейшим мы ее лучшим и обязательно избавимся от этого недостатка.

Но сейчас самое время остановиться и перевести дух. Выше были не самые тривиальные рассуждения и если ты чего-то не понял, то это совершенно нормально. Последовательностные схемы сложнее для восприятия и именно поэтому в предыдущей статье мы начали знакомство именно с комбинационной логики.

Поэтому советую перечитать несколько абзацев выше еще раз. Тем более, что это ключевая схема и далее в статье многие элементы будут основаны именно на ней. А вообще, самый правильный способ разобраться в любой схеме раз и навсегда — это взять ручку и листочек бумаги (или стилус и планшет) и последовательно рассмотреть каждый из возможных вариантов. Я сужу по личному опыту — в твоем случае может сработать что-то еще.

Практическое применение

Надеюсь, теперь принцип работы RS-триггера для тебя больше не секрет и тебе уже не терпится применить полученные знания на практике. Для этого понадобится микросхема IW4011, которая содержит четыре вентиля NAND (подойдет и любой зарубежный аналог).

Серия микросхем 4000 — это еще один прекрасный набор «строительных кирпичиков», которые раньше широко использовались при разработке устройств. В отличии от уже упоминавшегося семейства 7400, эти компоненты работают с расширенным диапазоном входных напряжений (до 15 Вольт). Следует помнить, что, хотя обе серии реализуют более-менее одинаковый набор логических схем, совместимость по выводам не гарантируется.

Наверняка ты уже знаком с таким неприятным явлением в электронике, как дребезг контактов. Он проявляется всякий раз, когда участки цепи коммутируются механически: при нажатии тактовой кнопки, переключении тумблера, реле и во многих других случаях. Как правило, с дребезгом предпочитают бороться программным способом: кратковременные изменения в сигнале (момент соприкосновения контактов) просто игнорируются устройством.

Это распространенный и достаточно эффективный способ: реализацию подобной функции можно найти и в Arduino (библиотека Bounce2). Однако у такого метода есть и свои минусы: обработку сигнала приходится задерживать на какое-то время (порядка нескольких десятков миллисекунд). Во многих случаях это не становится большой проблемой.

Но что, если нажатие на кнопку обрабатывается в прерывании? Или мы проектируем клавиатуру для геймеров и хотим получить минимальное время отклика? Да, «лишние» миллисекунды конечно не выведут тебя на первые строчки в ладдерах популярных игр, но некоторое преимущество точно обеспечат. Попробуем применить здесь RS-триггер и нарисуем такую схему.

Мы используем два вентиля NAND , то есть только «половину» микросхемы CD4011 (К561ЛА7). Обрати внимание, это не стандартная тактовая кнопка: тут работает перекидной контакт без фиксации, так что в каждый момент времени коммутируются ровно два вывода. Приятная особенность таких кнопок в том, что при нажатии они издают слабый щелчок, похожий на звук переключателей в механической клавиатуре.

Аппаратные решения хороши своей простотой и безотказностью — программа может зависнуть или исчерпать доступную память, тогда как с триггерами таких проблем нет.

Продвинутый D-триггер

Освоившись с установкой и сбросом внутреннего состояния в простой схеме, перейдем к более интересным вещам. Как и в программировании, теперь мы можем повторно использовать готовые логические блоки, чтобы эффективно абстрагироваться от возрастающей сложности устройств. Это примерно как с кодом — единожды реализовав нужную функцию или алгоритм, ты можешь добавлять их в необходимые места, не заботясь о стеке вызовов и конкретных адресах в памяти.

Как ты помнишь, ключевое неудобство в RS-триггере вызывал тот факт, что при nR = nS = 0 мы получали одинаковое состояние на прямом ( Q ) и, казалось бы, инверсном ( nQ ) выходе. Попробуем избавиться от этой проблемы. Для этого будем явно блокировать один из сигналов, если другой в этот момент активен.

Теперь состояние входа данных ( D ) через пару вентилей NAND подается на оба входа RS-триггера, а сигнал разрешения ( E ) контролирует момент времени, когда состояние правой половины схемы может меняться.

D-защелка — это почти как D-мейл, только защелка

Можно пойти еще дальше и объединить две защелки в один триггер, который будет срабатывать только по переднему фронту тактового сигнала (переход с низкого уровня в высокий). Это наиболее универсальная схема, так как позволяет мгновенно зафиксировать состояние всех сигналов на входных линиях, а уже потом приступить к формированию результата с помощью комбинационной логики.

Практическое применение

В 4000 серии пару D-триггеров реализует микросхема CD4013 (отечественный аналог — К561ТМ2). Назначение ее выводов ты можешь увидеть на схеме ниже. Обрати внимание, что, помимо входов данных и тактового сигнала, тут выведены контакты для асинхронного сброса и установки внутреннего состояния триггера.

Асинхронность означает, что событие происходит мгновенно, не дожидаясь следующего тактового сигнала. И наоборот, обновления с линии данных происходят синхронно с изменениями на линии CLK .

Таким образом, комбинируя микросхемы CD4011 (561ЛА7) и CD4013 (561ТМ2) можно собрать схему с тактовой кнопкой и светодиодом, которая будет помнить свое состояние. Первое нажатие заставит светодиод гореть, второе нажатие его погасит. При этом нам даже не потребуется микроконтроллер и мы не напишем ни строчки кода!

Кодовый замок на регистрах

Теперь пришло время для более серьезных вещей. Я собрал на макетной плате кодовый замок на микросхемах 561 серии. Часть из них ты уже знаешь, другую часть мы разберем в процессе.

Для удобства я сразу приведу принципиальную схему. Впрочем, ее всегда можно восстановить самостоятельно

Обрати внимание, что первая группа D-триггеров связана последовательно: инверсный выход через вентиль NAND блокирует тактовый сигнал следующего. Таким образом, пока не будет верно подобрана первая цифра ключа, остальная схема не будет реагировать на нажатия. Кроме того, на этот же вентиль подается инверсный выход самого триггера, так что как только нужная кнопка будет нажата в первый раз, блок отключается и далее внутреннее состояние D-триггера уже не меняется.

Отдельного рассмотрения заслуживает пара D-триггеров U3A и U6A . У них общий тактовый сигнал, а вход данных второго зависит от выхода первого. Так как изначально все триггеры сброшены в ноль, то даже после однократного нажатия нужной кнопки выход второго не изменится и последний из триггеров будет все также заблокирован (иными словами, ноль из U3A перекочует в U6A , но глобально это ничего не меняет).

Однако, первый регистр из пары все-таки поменяет свое состояние, так как по приходу тактового сигнала на его входе данных содержится логическая единица от инверсного выхода второго. Значит, на его выходе уже будет высокий уровень и нам потребуется еще один тактовый сигнал (нажатие на кнопку), чтобы протолкнуть «единичку» во второй регистр. Таким образом, можно сделать вывод, что одну из кнопок требуется нажать два раза подряд, после чего разблокируется последний D-триггер.

Кстати, трехвходовые вентили NAND для разрешения подачи тактового сигнала на D-триггер содержатся в микросхемах К561ЛА9 (по три штучки на корпус).

Разумеется, если взять такую схему отдельно, в ней будет существенный изъян: можно подобрать ключ, просто перебирая все кнопки одна за другой. В какой-то момент времени мы угадаем первую верную цифру, после чего перейдем ко второй, третьей и так далее.

Поэтому нам нужна возможность сброса состояния всех D-триггеров, как только превышено разрешенное количество попыток. Для этого требуется в первую очередь организовать подсчет, регистрируя нажатие любой цифры. Поэтому я взял парочку четырехвходовых вентилей NOR (К561ЛЕ6).

Логический ноль на их выходе образуется всякий раз, когда нажата какая-либо из подключенных кнопок. Объединим выходы вентилей с помощью операции И-НЕ. При этом сработает такое правило: инвертор на выходе логического элемента можно переместить на все его входы, но при этом поменяется и сам тип элемента ( NOR переходит в NAND и наоборот). Таким образом, NAND на выходе можно рассматривать как NOR , а инверторы на его входах оказываются рядом с инверторами на выходах блоков NOR и взаимно аннигилируют. В результате мы получаем один большой элемент OR , что и требовалось для нашего счетчика.

Кстати, схема самого счетчика выглядит так.

Он построен на базе трех D-триггеров, так что у нас три бита и восемь возможных состояний. Инверсный выход первого блока подается на вход, так что по восходящему фронту тактового сигнала BIT0 внутреннего состояния переходит из ноля в единичку (и наоборот). При этом выход соединен с CLK следующего и каждое второе переключение приводит к изменением для BIT1 .

Далее нам остается только отслеживать комбинацию 101 для пяти разрешенных попыток и подать сигнал сброса, если последний из D-триггеров, хранящих наш секретный код, все еще не оказался в состоянии логической единицы (случай правильной комбинации).

Работу всей схемы можно посмотреть на видео. Успешный код активирует таймер на микросхеме КР1006ВИ1, которая демонстрирует анимацию на светодиодной шкале.

Память (устройство, предназначенное для хранения данных и команд) является важной частью компьютера. Элементарной единицей компьютерной памяти является бит. Поэтому требуется устройство, способное находиться в двух состояниях, т.е. хранить единицу или ноль. Также это устройство должно уметь быстро переключаться из одного состояния в другое под внешним воздействием, что дает возможность изменять информацию. Ну и, наконец, устройство должно позволять определять его состояние, т.е. предоставлять информацию о своем состоянии. Устройством, способным запоминать, хранить и позволяющим считывать информацию, является триггер[1].

Триггер был изобретен в начале XX века М. А. Бонч-Бруевичем[2]. Разнообразие триггеров весьма велико. Наиболее простым является RS-триггер, который собирается из двух вентилей. Обычно используют вентили ИЛИ-НЕ или И-НЕ.

RS-триггер «запоминает», на какой его вход подавался сигнал, соответствующий единице, в последний раз. Если сигнал был подан на S-вход, то триггер на выходе постоянно «сообщает», что хранит единицу. Если сигнал, соответствующий единице, подан на R-вход, то триггер на выходе имеет 0. Не смотря на то, что триггер имеет два выхода, имеется в виду выход Q. (Q с чертой всегда имеет противоположное Q значение.)

Другими словами, вход S (set) отвечает за установку триггера в 1, а вход R (reset) – за установку триггера в 0. Установка производится сигналом, с высоким напряжением (соответствует единице). Просто все зависит от того, на какой вход он подается.

Большую часть времени на входы подается сигнал равный 0 (низкое напряжение). При этом триггер сохраняет свое прежнее состояние.

Возможны следующие ситуации:

- Q = 1, сигнал подан на S, следовательно, Q не меняется.

- Q = 0, сигнал подан на S, следовательно, Q = 1.

- Q = 1, сигнал подан на R, следовательно, Q = 0.

- Q = 0, сигнал подан на R, следовательно, Q не меняется.

Ситуация, при которой на оба входа подаются единичные сигналы, недопустима.

Как триггер сохраняет состояние? Допустим, триггер выдает на выходе Q логический 0. Тогда судя по схеме, этот 0 возвращается также и в верхний вентиль, где инвертируется (получается 1) и уже в этом виде передается нижнему вентилю. Тот в свою очередь снова инвертирует сигнал (получается 0), который и имеется на выходе Q. Состояние триггера сохраняется, он хранит 0.

Теперь, допустим, был подан единичный сигнал на вход S. Теперь в верхний вентиль входят два сигнала: 1 от S и 0 от Q. Поскольку вентиль вида ИЛИ-НЕ, то на выходе из него получается 0. Ноль идет на нижний вентиль, там инвертируется (получается 1). Сигнал на выходе Q становится соответствующим 1.

Архитектура ЭВМ (по книге В.Г. Баула[3] «Введение в архитектуру ЭВМ и системы программирования»)

Книга написана по читаемому автором в течение ряда лет лекционному курсу "Архитектура ЭВМ и язык Ассемблера" для студентов факультета Вычислительной математики и кибернетики Московского государственного университета имени М.В. Ломоносова

Всех людей, которые, так или иначе, используют компьютеры в своей деятельности и имеют понятие об их архитектуре, обычно называют пользователями. Ясно, что в зависимости от того, на каком уровне они видят архитектуру компьютера, всех пользователей можно, хотя, конечно, и достаточно условно, разделить на уровни или группы. Как правило, выделяют следующие группы пользователей.

Для вводного курса достаточно внешнего уровня, возможно, с элементами концептуального уровня и минимальным знакомством с внутренним уровнем.

Теперь уточним эти принципы и состав машины. На рис. 1 приведена схема машины фон Неймана[4], как она изображается в большинстве учебников, посвященных архитектуре ЭВМ.

Рисунок 1. Схема машины фон Неймана

На этом рисунке толстыми (двойными) стрелками показаны потоки команд и данных, а тонкими – передача между отдельными устройствами компьютера управляющих и информационных сигналов.

Читайте также: