Программы для программирования плис

Обычно, когда кто-то видит функционирующую плату, всегда задают одни и те же вопросы: - Это Ардуино? - А как это работает без Ардуино?

Это не микроконтроллер, это даже не процессор, это ПЛИС. ПЛИС - это программируемая логическая интегральная схема, такая микросхема состоит из множества одинаковых блоков или макроячеек, каждый производитель по своему их называет, так у Xilinx это Slices (ломтики) у Altera - LogicElements (логические элементы). Эти блоки относительно простые, они могут выполнять роль нескольких логических элементов, быть маленькой таблицей поиска (LUT), содержать готовый сумматор, умножитель, блок цифровой обработки сигналов (DSP), в общем все что задумает производитель. Пользователь может по своему желанию расположить и настроить эти блоки как ему захочется, реализовав таким образом достаточно сложные цифровые схемы. На ПЛИС можно реализовать хоть микроконтроллер, реализовав например ту же Ардуино или процессор вашей собственной архитектуры, например не регистровый а стековый процессор, даже свою собственную ПЛИС можно реализовать на ПЛИС!

Из доступных бюджетных ПЛИС можно выделить двух основных производителей Altera и Xilinx, с их продукции можно начать свой путь освоения данных технологий. На мой взгляд лучше выбрать чипы компании Altera, так как их среда проектирования стабильно обновляется, а выбрав один популярный чип Xilinx XC3S500E вам придется довольствоваться устаревшей средой ISE 14.7 (хотя и там есть свои плюсы).

В иностранной литературе можно встретить сокращения для ПЛИС: FPGA и CPLD. CPLD (Complex Programmable Logic Device ) - чипы с небольшим числом макроячеек, специализированных блоков и малым энергопотреблением. Большой проект не получится синтезировать для такого типа чипов, но и для них находят применение на практике, так у редкого микроконтроллера найдется, скажем 300 ножек. Такие чипы часто применяют в качестве интерфейсных систем, предобработчиков, расширителей ввода-вывода. FPGA (Field-Programmable Gate Array) - программируемая пользователем вентильная матрица (ППВМ), значительно более мощные чипы по сравнению с CPLD, но потребляющие больше энергии и стоящие значительно дороже. Для уменьшения затрат площади кристалла FPGA чипы могут содержать уже готовые функции, такие как блоки цифровой обработки сигналов (DSP блоки), встроенные процессоры, встроенная память. FPGA широко применяются для проверки и верификации проектов, в так называемой докремниевой проверке пригодности, тем самым уменьшая затраты и время перед выходом продукта. FPGA чипы могут быть переконфигурированы практически в любой момент времени, сейчас ведутся разработки, например в Intel, по совмещению архитектур обычного процессора и чипа FPGA. У Xilinx уже есть такие решения - Zynq, но о них мы пока не будет вести речь.

Разговор пойдет о более простых вещах, тем более ко мне в руки попал набор разработчика: Cyclone IV 4 FPGA Core Board и Altera USB Blaster Downloader PLD Development kit за 35$, приобретенный на AliExpress.

1 Демоплата Cyclone IV 4 FPGA Core Board, краткая характеристика

Рис. 1 - Демоплата Cyclone IV 4 FPGA Core Board

На плате (Рис. 1) установлен чип EP4CE6E22C8N, его характеристики:

| Вид ресурса | Краткое описание | Количество |

|---|---|---|

| Logic elements (Les) | Число логических блоков - ячеек, основная характеристика, по которым мы можем сравнивать «мощность» чипов, любая синтезированная логика будет затрачивать данные блоки | 6,272 |

| Embedded memory (Kbits) | Встроенной памяти, пока для нас не важная характеристика | 270 |

| Embedded 18x18 multipliers | Встроенных аппаратных умножителей, очень важный параметр в цифровой обработке сигналов, вся мощь ПЛИС раскрывается, когда несколько умножителей работают параллельно | 15 |

| General-purpose PLLs | Узлов фазовой автоподстройки частоты, пока не важная характеристика, упрощает синхронизацию устройств, работающих на разных частотах | 2 |

| Global Clock Networks | Количество частотных доменов, пока не важная характеристика | 10 |

| User I/O Banks | Число раздельных пользовательских банков ввода-вывода, пока не важная характеристика | 8 |

| Maximum user I/O | Число пользовательских пинов ввода-вывода, мы можем подключить любые устройства, как например к Ардуино | 91 |

На плате установлено:

- Флэш память – при подаче питания ПЛИС будет сконфигурирована в реализацию во флеш памяти. Вы можете синтезировать свой проект и записать в эту флэш

- Кварц 25 Мгц – генератор опорной тактовой частоты, именно на этой частоте будут работать все наши проекты, наша ПЛИС может поддерживать до 10 таких каналов.

- Светодиоды – 10, кнопки – 2.

- Пины ввода-вывода 61 + 2 земля, 1 не соединен. Можно подключить разнообразные устройства. ЦАП-АЦП, акселерометры и гироскопы, символьный и графические дисплеи, как и у Ардуино.

- Питание через USB, или внешнее 5В.

В комплекте также идет программатор JTAG, Altera USB Blaster.

2. Среда Quartus II и наш первый проект

Рис. 2 - выбираем необходимые продукты Altera

И жмем кнопку скачать (Download Selected Files). После чего нам предложат зарегистрироваться, регистрируемся, скачиваем и устанавливаем.

Создадим свой первый проект.

Запускаем Quartus, выбираем главное меню File -> New Project Wizard, появляется окно введения, жмем next. Далее нужно указать каталог для проекта и его имя, третье поля – имя верхнего модуля, попозже увидите, что это. Выбираем папку, куда хотим сохранить проект и придумываем имя, у меня test1.

Рис. 3 - окно мастра нового проекта

Жмем next, у нас спрашивают, пустой проект (empty project) или шаблон (Project template). Оставляем пустой, next. Дальше нас просят добавить существующие файлы, у нас ничего нет, поскольку мы только начинаем свой путь, жмем next.

Далее нам необходимо выбрать наш чип, это можно сделать в любое время. Выбираем как на рисунке, Family – Cyclone IV E, specific device selected in “Available devices” и выбираем наш чип EP4CE6E22C8N, он в самом начале. Если у вас другой, найдите свой, это важно. Жмем next.

Рис. 4 - Окно мастера нового проекта, выбор нужного чипа

Появится окно - выбора средств проектирования, отладки, пока это пропускаем, нажимаем next и затем finish.

Далее главное меню Assignments -> Device, здесь можно выбрать чип (нашу ПЛИС), выбираем если не выбрали, нажимаем кнопку «Device and Pin Options».

Рис. 5 - Окно « Assinments-Deice »

В окне выбираем пункт «Unused pins». Эта настройка определяет, что будет с неподключенными пинами. Это может быть важно, в своем проекте вы вряд ли используете все пины, а не подключенные могут быть на деле соединены с землей или питанием (ну мало ли, кто разводил плату). Если вы подадите единичку на заземленный пин, то он сгорит, поэтому нужно внимательно следить за этим.

Рис. 6 - Окно « Device and Pin Options » , Unused Pins

Далее нам нужно настроить пины, это нужно чтобы сигнал шел на нужные нам ножки чипа, ведь изначально Quartus не знает, что куда подключено и как именно осуществлена разводка платы.

Подключаем это все в «Assignment Editor»

Рис. 7 - Вызов « Assignment Editor » из меню или панели

В появившемся окне делаем как у меня, ну или если совсем правильно, то согласно схеме вашей платы.

Рис. 8 - Assinement Editor

В колонке «To» вписываем имя входа или выхода. В колонке «Assignment Name» выбираем «Location». В колонке «Value» номер контакта микросхемы, согласно схемы платы (у меня номера пинов написаны прямо на плате).

Также нужно указать, что делать с кнопками, которые одной ногой подключены к земле, а другой ко входу чипа. При нажатии на ноге будет низкий уровень, а вот без нажатия, непонятно, нога чипа будет просто висеть в воздухе, что очень плохо. Нужно подтянуть к питанию вход чипа либо резистором на плате, либо боле элегантным способом в «Assignments Editor». В колонке «Assignment Name» выбираем «Weak Pull Up resistor» для группы key* (группа обозначается через звездочку).

Рис. 9 - Assignment Editor

Далее нужно создать описание модуля верхнего уровня, который будет работать непосредственно с ножками чипа, все остальные модули будут работать только с ним. В главном меню жмем New, и выбираем "Design Files-> Block Diagram/Schematic File".

Рис. 10 - Диалог новых файлов

В открывшемся окне выбираем инструмент «Pin Tool» и располагаем вход и выход (пины ввода и вывода) на диаграмме. Переименовываем вход как key[0], выход как led[0] и соединяем их проводником. Сохраняем и нажимаем "Start Compilation".

Рис. 11 - Окно графического описания, выделены Pin Tool и Start Compilation

После компиляции у нас возникли предупреждения, пока игнорируем их, они касаются неподключенных пинов, отсутствия тактового сигнала и описания для «Timing Analyzer».

Подключаем демоплату и программатор, выбираем инструмент «Programmer». В окне должно значиться «USB-Blaster [USB-..]», если нет то нажимаем «Hardware Setup» и пытаемся разобраться почему нет, скорее всего не установлены драйвера, смотрим в устройства Windows, ищем неопределенные устройства, может с кабелем проблема. Если все хорошо нажимаем «Auto Detect» и выбираем наш чип.

Рис. 12 - Окно Programmer

Нажимаем двойным щелчком мыши в поле «File» и выбираем файл для записи на ПЛИС (находиться в папке output_files нашего проекта), ставим галочку в поле «Program / Configure», и нажимаем кнопку «Start».

Рис. 13 - Окно Programmer, наш чип уже сконфигурирован

Поздравляю с первой конфигурацией ПЛИС! Диод D1 должен светиться, при нажатии key1 должен гаснуть (так как кнопка замыкает ножку с землей), далее мы с этим что-нибудь сделаем)

Первые ПЛИС можно было сконфигурировать, просто задав положение всех электронных ключей вручную. (Сомнительно, что так делали даже тогда, но теоретически это было возможно). Сейчас же разработка конфигурационной прошивки для ПЛИС, настраивающей ее на выполнение требуемой заказчику функциональности - процесс сложный и многоэтапный. Начинается он, как правило, с описания функциональности устройства на языке высокого уровня. Чаще всего это Verilog либо VHDL, но в последнее время это может быть и C/C++, а так же результаты работы таких программ, как Matlab/Simulink либо LabView.

Слово «программирование» взято в кавычки, т.к. под ним понимается процесс, приводящий в конечном этапе к некоторой функциональной конфигурации ПЛИС, в отличие от программирования для процессорных систем, где программирование – это задание на некотором языке последовательности выполнения действий. Соответственно, основные языки, используемые для задания функциональности ПЛИС – Verilog/SystemVerilog и VHDL, в строгом смысле не являются языками программирования и их называют «языками проектирования аппаратуры» (HDL – Hardware Design Language).

Языки проектирования аппаратуры

Несмотря на явный сдвиг в сторону высокоуровневого проектирования, полностью потенциал программируемой логики можно раскрыть только на классических языках проектирования аппаратуры. Таковых существует всего два – Verilog/SystemVerilog (разработан 1984/2002 гг.) и VHDL (разработан 1983 г.). Эти языки полностью функционально эквивалентны, но имеют абсолютно различный синтаксис. Общие черты HDL-языков:

- Имеют синтезируемое и несинтезируемое подмножество операторов. Именно синтезируемые операторы, описывающие функциональность реальной аппаратуры отличают HDL-языки от обычных языков программирования. В то время как несинтезируемое подмножество используется для симуляции и тестирования и мало отличается от алгоритмических языков программирования.

- Используются для описания параллельно выполняющихся действий.

Отличия:

Verilog/SysnemVerilog по синтаксису похож на язык C, а синтаксис VHDL основан на языке ADA.

В нижеследующей таблице приведены варианты кода на языках Verilog и VHDL для описания простого логического элемента – счетчика с предварительной загрузкой.

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all; -- for the unsigned type

entity COUNTER is

generic (

WIDTH : in natural := 32);

port (

RST : in std_logic;

CLK : in std_logic;

LOAD : in std_logic;

DATA : in std_logic_vector(WIDTH-1 downto 0);

Q : out std_logic_vector(WIDTH-1 downto 0));

end entity COUNTER;

architecture RTL of COUNTER is

signal CNT : unsigned(WIDTH-1 downto 0);

begin

process(RST, CLK) is

begin

elsif rising_edge(CLK) then

CNT <= unsigned(DATA); -- type is converted to unsigned

else

end if;

end if;

end process;

Q <= std_logic_vector(CNT); -- type is converted back to std_logic_vector

end architecture RTL;

Видно, что описание на Verilog значительно компактнее кода на VHDL, поэтому сейчас язык Verilog используется чаще, чем VHDL. Среди недостатков «чистого» Verilog, часто отмечают отсутствие объектно-ориентированного подхода (при том, что VHDL изначально разрабатывался как объектно-ориентированный язык), но появление языка SystemVerilog полностью устранило этот недостаток. САПР Vivado изначально поддерживает как Verilog/SystemVerilog, так и VHDL, причем в проекте эти языки можно применять одновременно.

Проектирование на языках HDL является стандартным классическим подходом к проектированию, но этот подход отнюдь не единственный. Сейчас получает широкое распространение и популярность т.н. «высокоуровневое проектирование», т.е. разработка аппаратной части системы на высокоуровневых языках программирования, прежде всего – на языках C/C++. Ниже будут рассмотрены несколько широко применяемых при проектировании ПЛИС и СнК маршрутов проектирования.

Экологическая система ПЛИС и СнК

Чтобы эффективно использовать ПЛИС, кроме самой микросхемы, требуется много дополнительных средств, составляющих экосистему разработки и применения ПЛИС.

Прежде всего, к экосистеме ПЛИС относятся программные средства разработки, но также в нее входят jtag-кабели для прошивки и отладки ПЛИС (иногда их называют «программаторами»), отладочные платы и средства, документация и демодезайны, различные форумы разработчиков, производство коммерческих и свободных IP-ядер и многое другое. Так же с 1988 года и по сей день Xilinx издает бесплатный виртуальный XCell Journal, доступный для скачивания в виде pdf-файла.

Средства разработки

Средства разработки для ПЛИС и СнК являются неотъемлемой частью инфраструктуры ПЛИС и в этой области Xilinx удерживает лидерство, постоянно развивая и улучшая свои программные продукты.

Первые релизы средств разработки Xilinx уже мало кто помнит, но в первом выпуске Xcell Journal они упомянуты – это XACT и XACTOR:

САПР ISE получился очень удачным и, в том числе, даже по личному опыту, могу сказать, что разработчики его любили. Завершающей версией ISE стал релиз 14.7 от октября 2013 года, когда разработка была прекращена, а проект был заморожен. Однако микросхемы, для которых требуется ISE, все еще серийно выпускаются, поэтому ISE используется даже сейчас. Возможно (но это неточно), что это рекорд продолжительности жизни для САПР!

Следующим САПР от Xilinx стал пакет Vivado, выпущенный в 2014 г., интерфейс которого был создан на базе оболочки PlanAhead из ISE. Данный САПР завершил свою активную фазу в 2019г., когда был выпущен релиз под номером 2019.1.

Далее, с версии 2019.2, представленной в ноябре 2019 г., Xilinx перешел на САПР Vitis, а Vivado вошел в него составной частью.

Таким образом, на данный момент мы имеем уже пятое поколение средств разработки от Xilinx.

Маршруты проектирования ПЛИС

Классический маршрут

Если по данному маршруту проектируется система на кристалле, содержащая процессорную часть, то на выходе мы имеем готовую вычислительную систему, программирование для которой осуществляется стандартными программными средствами.

Расширением данного маршрута является проектирование с применением IP-ядер. IP-ядро можно сравнить с API в программировании. Это ранее разработанная и отлаженная часть проекта, выполняющая определенную функциональность. IP-ядра можно хранить отдельно в специальных репозиториях и включать в свои проекты по мере необходимости. Данный маршрут можно считать основным в САПР Vivado:

Соответственно, маршрут проектирования с использованием IP-ядер немного меняется:

Именно этот маршрут проектирования реализован в среде проектирования Vivado.

Визуальное проектирование с использованием IP-репозитория

Этот способ проектирования наиболее распространен для проектирования систем на кристалле (т.е. систем с процессорными ядрами), но может применяться и для обычных ПЛИС. В Vivado этот способ широко применяется, причем можно создавать иерархические графические диаграммы и заполнять их из репозиториев различными компонентами. Собственные модули на языках Verilog и VHDL также можно вставлять в эти диаграммы.

Высокоуровневое проектирование

Следующий маршрут проектирования – так называемое «высокоуровневое проектирование», ниже показана диаграмма для этого маршрута. Здесь алгоритм, описываемый на C/C++, реализуется в программируемой логике в виде IP-ядра. Затем это IP-ядро может быть включено в любой проект. А весь проект имплементирован по классическому маршруту.

Имеется еще один высокоуровневый маршрут проектирования, применяемый для систем на кристалле. Данный маршрут проектирования является стандартным в новейшем САПР Vitis.

Этот маршрут проектирования начинается с написания программы на C/C++. Затем производится профилирование программного кода и определение функций, замедляющих работу системы. С целью повышения скорости работы этих функций они реализуются в программируемой логике и, при необходимости, подвергаются дальнейшей оптимизации.

Новейшая среда разработки Vitis (на рис выше) предназначена для проектирования на самых современных системах на кристалле Xilinx, включая выводимое на рынок семейство Versal, а также для ускорительных платформ Alveo.

Среда разработки Vitis™ AI - это платформа разработки Xilinx для вывода ИИ на аппаратных платформах Xilinx

Vitis позволяет решать самые сложные задачи в различных предметных областях, включая разработку систем искусственного интеллекта. Это достигается путем интеграции Vitis со специализированными пакетами. Например, для разработки систем искусственного интеллекта на базе ПЛИС и СнК Xilinx , используется пакет VitisAI , структура которого показана ниже.

Анализируя маршруты проектирования, можно сделать вывод, что проектирование для программируемой логики движется в сторону сближения с классическим программированием. Это позволяет расширить применение программируемой логики за счет привлечения программистов, которым не нужно разбираться в тонкостях архитектуры ПЛИС.

Отметим также, что классические маршруты проектирования реализуют методику «снизу-вверх», т.е. сначала разрабатывалась аппаратная часть, производилась ее верификация сначала на уровне блоков и модулей, а затем полностью собранная система. Затем для этой системы можно было разрабатывать программное обеспечение. В то же время методология высокоуровневого проектирования наиболее эффективна при реализации метода «сверху вниз», т.е разработка начинается с создания и отладки программного обеспечения, а аппаратная часть конфигурируется уже под требования разработанного программного продукта.

Выводы:

Компании на данный момент удалось создать наиболее совершенные и мощные средства проектирования в отрасли. Однако для полного раскрытия потенциала этих средств требуется их квалифицированное применение, а для этого, в свою очередь, компаниям необходимо регулярно повышать квалификацию своих ведущих разработчиков.

Вебинар: Начало работы с Xilinx Vivado HLS

Автор: Викулин Владимир, инженер по применению Xilinx компании Макро Групп.

Обновление Март 2021 года.

Обучение проектированию и программированию ПЛИС в системе Vivado

Компания МакроГрупп совместно с компанией PLC2 – европейским лидером в обучении технологиям проектирования на ПЛИС и СнК, открывает программу обучения российских специалистов по программам и при участии PLC2. Выдается сертификат от компаний МакроГрупп и PLC2.

На данный момент доступны учебные курсы, посвященные маршруту проектирования Vivado:

- Введение в проектирование в системе Vivado

- Проектный маршрут проектирования в Vivado

- Применение TCL в Vivado (Несколько курсов)

- Непроектный маршрут в Vivado

- Маршрут ECO в Vivado

В дальнейшем номенклатура учебных курсов будет существенно расширена.

Обучение доступно в виде онлайн-вебинаров, очных тренингов, также возможно проведение корпоративных тренингов. Приглашаем компании и заинтересованных в дополнительном профессиональном обучении специалистов принять участие в тренингах в удобном для Вас формате.

В течение многих лет с момента освоения коммерческого производства программируемых логических кристаллов архитектуры FPGA корпорация Altera (США) занимает второе место на рынке ПЛИС, все это время успешно конкурируя с лидером рынка — американской фирмой Xilinx. В области развития существующих архитектур программируемой логики и разработки новых семейств ПЛИС сложно определить абсолютного лидера из двух упомянутых конкурентов, ибо продукция корпорации Altera нередко превосходит аналоги по техническим и экономическим показателям. Все программируемые пользователем микросхемы производства корпорации Altera, включая ПЛИС архитектуры FPGA, ПЛИС архитектуры CPLD и энергонезависимую память конфигурации FPGA, поддерживают внутрисхемное программирование — ISP (In-System-Programming). Технология внутрисхемного программирования предоставляет возможность изменять конфигурацию компонентов устройства без их демонтажа. Иными словами, осуществлять программирование микросхем не на программаторах, а непосредственно в устройстве.

Для внутрисхемного программирования ПЛИС архитектур FPGA и CPLD корпорации Altera применяется диагностический последовательный интерфейс JTAG [1]. Этот интерфейс состоит из четырех или пяти логических сигналов: TCK, TMS, TDI, TDO и TRST (необязательный). Уровни сигналов интерфейса JTAG не регламентированы и зависят от технологических особенностей микросхем. Вопросы организации взаимодействия в объеме одного устройства логических микросхем с различными уровнями сигналов, например выходов на 3,3 В с входами на 5 и 1,5 В, широко отработаны и в этой статье не рассматриваются.

Для обеспечения внутрисхемного программирования сигналы JTAG-интерфейса выводятся на специальный разъем, предназначенный для подключения загрузочных кабелей и адаптеров, играющих роль устройств сопряжения между цепочкой микросхем и компьютером, на котором работают системы проектирования.

Для внутрисхемного программирования микросхем энергонезависимой памяти, не поддерживающих интерфейс JTAG и предназначенных для хранения конфигурации FPGA, (микросхемы Serial Configuration DevicesEPCS1, EPCS4 EPCS16, EPCS64, EPCS128) применяется технология внутрисхемного программирования в режиме Active Serial, использующем семь сигналов в отличие от четырех сигналов JTAG [3].

Корпорация Altera выпускает несколько типов загрузочных кабелей для конфигурации в ПЛИС как по интерфейсу JTAG, так и в режимах последовательной загрузки FPGA (Active Serial и Passive Serial). Наиболее простыми с точки зрения производства являются кабели для параллельного порта LPT. Кабель ByteBlaster поддерживает внутрисхемное программирование ПЛИС в режимах JTAG и Passive Serial [4, 5]. Усовершенствованная версия кабеля ByteBlaster II поддерживает три режима: JTAG, Passive Serial и Active Serial [6]. Оба кабеля используют одинаковый технологический разъем IDC-10 для подключения к целевому устройству.

Кабель Altera ByteBlaster оснащен штыревым соединителем IDC-10 / BH-10 (ответная часть), с одним удаленным контактом (8), играющим роль ключа. В кабеле ByteBlaster II использован аналогичный соединитель без отсутствующего контакта-ключа, так как все пустовавшие контакты разъема задействованы для сигналов режима Active Serial. Разводка технологического разъема для программирования ПЛИС Altera показана на рис. 1: здесь представлен вид со стороны отверстий соединителя IDC-10.

Рис. 1. Разъем IDC-10 загрузочного кабеля для конфигурации ПЛИС Altera (вид со стороны отверстий)

Со времен IBM PC персональные компьютеры, серверы и рабочие станции оборудовались периферийным интерфейсом параллельного порта — LPT. В настоящее время этот интерфейс вытеснила шина USB, но при необходимости он может быть добавлен в конфигурацию компьютера при помощи установки адаптеров расширения стандарта PCI или PCI Express. Краткое описание интерфейса LPT-порта приведено в [7].

Взаимодействие с программируемыми кристаллами по последовательному интерфейсу конфигурации FPGAили JTAG через порт LPT реализовано исключительно программным способом, наподобие работы с портами GPIO современных микроконтроллеров. Драйвер, входящий в состав САПР, путем обращения к регистрам адаптера LPT формирует на выводах порта последовательность логических сигналов, соответствующую протоколу обмена с конфигурационной цепочкой ПЛИС. Сигналы Active Serial и JTAG могут быть получены из сигнальных линий LPT-порта при помощи буферов-повторителей. Большинство схем сопряжения с интерфейсами внутрисхемного программирования через параллельный порт построены на микросхемах КМОП серий 74HC/74HCT/74AHC/74AHCT (а именно 74HC125, 74HCT125, 74HC244, 74HCT244) и им подобных.

Буферные микросхемы в составе загрузочного кабеля обеспечивают усиление принятых сигналов по току и уровню напряжения и реализуют дополнительную защиту ПЛИС в составе целевого устройства от протекания сквозных токов, вызванных перепадами потенциалов между корпусами устройств и различными наводками.

Соответствие сигналов JTAG и Active Serial сигнальным линиям и контактам разъема LPT-порта для загрузочных кабелей ByteBlaster и ByteBlaster II корпорации Altera приведено в таблице. Через дробь указаны сигналы двойного назначения: в числителе — сигнал Active Serial, в знаменателе — сигнал JTAG.

Разъем DB-25M

Сигнал, формируемый или анализируемый САПР Altera Quartus II

Примечание: Насколько я смог выяснить, в русском языке на сегодняшний день термины ПЛИС и FPGA (Field-Programmable Gate Array, Программируемая Пользователем Вентильная Матрица), принято считать взаимозаменяемыми, что будет использовано далее по тексту. Однако стоит знать о существовании и альтернативной точки зрения, согласно которой FPGA (ППВМ) является одной из разновидностей ПЛИС (PLD, Programmable Logic Device).

Основные сведения об FPGA

На данный момент лидирующими производителями FPGA являются компании Altera (сейчас принадлежит Intel) и Xilinx. По информации из разных источников, вместе они контролируют не менее 80% рынка. Из других игроков стоит отметить Actel (куплена Microsemi), Lattice Semiconductor, Quicklogic и SiliconBlue. С железом от Xilinx можно работать только из среды разработки от Xilinx (называется Vivado), а среда разработки от Altra (называетя Quartus) понимает только железо от Altera. То есть, полный вендор лок, и выбирая конкретную FPGA для своего проекта, вы автоматически выбираете и инструменты разработки соответствующего производителя, их техническую поддержку, документацию, условия лицензирования софта, политику касаемо прекращения поддержки железа, и так далее.

FPGA часто используются в задачах, где некие вычисления хочется существенно ускорить, реализовав их прямо в железе. Например, FPGA нашли широкое применение в области обработки сигналов, скажем, в осциллографах, анализаторах спектра, логических анализаторах, генераторах сигналов, Software Defined Radio и даже некоторых мониторах. В частности, в LimeSDR используется Altera Cyclone IV, а в осциллографе Rigol DS1054Z стоит Xilinx Spartan-6, а также ProASIC 3 от компании Actel. Еще из применений, о которых я слышал, могу назвать компьютерное зрение, распознавание речи и биоинформатику. Есть и другие проекты, в частности по разработке веб-серверов и СУБД, работающих на FPGA [PDF]. Но, насколько мне известно, это направление все еще остается сильно экспериментальным.

Xilinx или Altera?

Как говорится, лучший Linux тот, который использует ваш знакомый гуру по Linux.

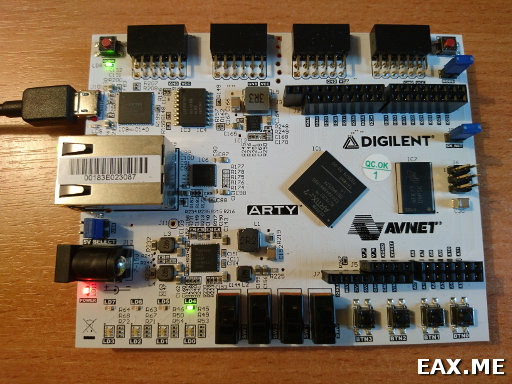

Мой знакомый гуру по FPGA в лице Дмитрия Олексюка посоветовал начать с девборды Arty Artix-7 от компании Digilent. Используемой в ней FPGA является Artix-7 от Xilinx. Сам Digilent не производит доставку в Россию, но устройство доступно и на AliExpress, хотя и с заметной наценкой (официальная цена составляет 99$). Также его продают на eBay. Это довольно мощная плата, которая, тем не менее, стоит вполне адекватных денег.

Fun fact! Если вам просто хочется попрограммировать на Verilog или VHDL, строго говоря, покупать какую-либо плату с FPGA не требуется. Первое время можно ограничиться симулятором, работа с которым будет рассмотрена далее.

Из интересных особенностей платы можно назвать расположение гнезд совместимым с Arduino-шилдами способом. Также в комплекте с платой идет вкладыш, по которому можно получить лицензию на Vivado, открывающую все его возможности. Лицензия действует один год с момента активации, а также привязана к одному компьютеру по типу ОС и MAC-адресу.

По доставке. Я слышал, что устройства с FPGA на борту имеют большие шансы не пройти таможню. Магазин на AliExpress, ссылку на который я привел выше, доставляет платы в Россию через курьерскую службу СПСР. Для прохождения таможни потребовалось заполнить онлайн-форму с паспортными данными (только данные, без фото) и контактным телефоном, как этого требует текущее российское законодательство. После этого плата была доставлена курьером прямо до двери без каких-либо вопросов.

Установка Vivado

Среда разработки Vivado доступна для скачивания на сайте Xilinx. Будьте морально готовы к тому, что перед скачиванием вам придется пройти регистрацию и заполнить довольно подробную форму о себе. Скачиваем архив под названием «Vivado HLx 2017.2: All OS installer Single-File Download». Не перепутайте случайно с каким-нибудь «Vivado Lab Solutions», это совершенно не то, что нужно. Архив весит более 20 Гб, поэтому запасаемся терпением.

Распаковываем архив, запускаем инсталлятор. Ставим Vivado HL System Edition. Полная его версия займет на диске 47 Гб. Лично я снял галочку напротив Software Development Kit и оставил поддержку только 7 Series устройств, что уменьшило размер до 12 Гб. Забегая немного вперед отмечу, что такой конфигурации оказалось вполне достаточно.

Перед запуском Vivado нужно добавить в него поддержку Arty Artix-7, так как из коробки он ничего об этой плате не знает. Делается это как-то так:

Также скачиваем отсюда и сохраняем куда-нибудь файл Arty_Master.xdc. Он понадобится нам далее. Файл содержит описание находящихся на плате светодиодов, переключателей и так далее. Без него поморгать светодиодами на Verilog будет непросто.

Первый проект на SystemVerilog

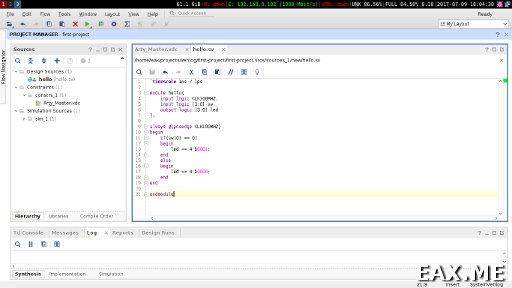

В дереве исходников находим новый файл hello.sv, он будет в группе Design Sources. Открываем и пишем следующий код:

`timescale 1ns / 1ps

Если все было сделано правильно, на этом этапе Vivado у вас будет выглядеть как-то так (кликабельно, PNG, 71 Кб):

Запустим синтез, сказав Flow → Run Synthesis, или просто нажав F11. В правом верхнем углу вы увидите индикацию того, что процесс идет. Он может занимать довольно много времени, в зависимости от вашего компьютера и сложности программы. На моем ноутбуке синтез приведенной выше программы выполнился где-то секунд за 10. Если теперь сказать Flow → Open Synthesized Design, то можно увидеть красивую картинку вроде такой:

Настало время прошить нашу плату. Говорим Flow → Run Imlementation, затем Flow → Generate Bitstream. Подключаем плату к компьютеру по USB, в Vivado говорим Flow → Open Hardware Manager → Open target → Auto Connect → Program device. Потребуется указать путь к bit-файлу. У меня он был следующим:

Говорим Program. Теперь на плате горит светодиод LD4, если переключатель SW0 опущен (см приведенную выше фотографию платы). Если же переключатель поднят, светодиод не горит. Простенько, конечно, но это же «hello, world», чего вы ожидали? :)

Симуляция

При знакомстве с симуляцией первое, что я обнаружил, было то, что она у меня не работает. В логах было просто:

ERROR: [XSIM 43-3409] Failed to compile generated C file [. ]xsim_1.c.Google по этой ошибке находил только всякую ерунду в стиле «попробуйте отключить антивирус». В итоге решить проблему помогло добавление флага -v 2 в скрипт

/opt/xilinx/Vivado/2017.2/bin/xelab. С его помощью я выяснил, что Clang, бинарник которого Vivado таскает за собой, падает со следующей ошибкой:

/a/long/path/to/clang: error while loading shared libraries:libncurses.so.5: cannot open shared object file: No such file or

directory

А эта ошибка и ее решение уже описаны на Arch Wiki. Лично я просто скопировал уже существующий файл из каталога Vivado_HLS:

По аналогии с тем, как ранее мы создавали hello.sv, создаем новый файл hello_sim.sv в группе Simulation Sources. В файле пишем следующий код:

`timescale 1ns / 1ps

В дереве исходников делаем правый клик по файлу, выбираем Source Node Properties. В секции Used In снимаем галочки Synthesis и Implementation. Мы же не хотим, чтобы какие-то там тесты засоряли нашу далеко не резиновую FPGA?

Теперь говорим Flow → Run Simulation → Run Behavioral Simulation. В итоге вы увидите что-то примерно такого плана:

Можно видеть, что когда sw[0] равен нулю, led[0] равен единице, и наоборот. При этом все изменения происходят по фронту тактового сигнала. Похоже, что программа работает корректно. Ну и на ассертах ничего не свалилось, что как бы намекает.

Заключение

Архив с описанным выше проектом можно скачать здесь. В качестве дополнительных источников информации я бы рекомендовал следующие:

А пишите ли вы под FPGA? Если да, то на каком языке и какого производителя предпочитаете?

Для создания файла конфигурации устройства, работающего по формуле c=|a+b|

на базе ПЛИС Xilinx Virtex5 xc5vlx50 создаем новую модель в программе Матлаб (Рис. 1).

После создания модели открываем Библиотеку элементов Simulink (Рис. 2).

Для создания проекта любой модели Simulink для ПЛИС необходимо присутствие элемента System Generator (Рис. 3), который является связующим звеном между программными средами Simulink и Xilinx 11, а также позволяет генерировать проект

для Xilinx 11 и работать с отладочными устройствами.

Добавляем в модель элемент System Generator, для чего необходимо открыть раздел библиотеки элементов Simulink (Xilinx Blockset -> Basik Elements) (Рис. 3) и разместить необходимый элемент в окне модели.

Также в модель нужно добавить остальные элементы для реализации проекта (Рис. 4).

В связи с тем, что в составе стандартных библиотечных элементов Xilinx отсутствует элемент вычисления модуля числа (поэтому и была выбрана именно эта элементарная функция), для конфигурации этой части функции можно использовать элемент MCode. Для конфигурации элемента MCode, необходимо в папке содержащей файл модели создать М-файл с текстом (М-файл это обычный текстовый файл с расширением ".m" в данном случае «abs_xil.m», вообще имя файла должно быть таким-же как имя функции, Матлаб любит это;) более подробное описание языка М-файлов можно посмотреть покурив хелп матлаба, а при знании С/С++ проблем вообще не возникнет ):

Далее в настройках элемента MCode (Рис. 5) (открываются двойным щелчком левой кнопки мыши) необходимо нажать Browse… выбрать созданный М-Файл и нажать «ОК».

После чего элемент MCode примет вид согласно Рис. 6.

Измененный элемент MCode теперь выполняет функцию вычисления модуля числа,

М-Файл, используемый в данном блоке можно изменять и редактировать (например, формат выходных данных). (Для каждой новой модели рекомендуется создавать отдельную копию соответствующего М-Файла).

Теперь необходимо соединить все элементы модели указанным на Рис. 7 способом.

Для просмотра действия модели необходимо добавить входные данные и возможность просмотра результатов.

Настроим модель согласно Рис. 8, (всякие кубики генераторов и осцилографов можно взять в стандартной библиотеке Симулинка в разделе Simulink) параметры генераторов Sine Wave и Sine Wave 1, указаны на Рис. 9.

После запуска симуляции проекта, на экране осциллографа можно посмотреть входные сигналы, промежуточный и выходной результаты (Рис. 10).

Во время построения модели использование стандартных библиотечных элементов Simulink совместно с библиотечными элементами Xilinx невозможно (при генерации проекта, элементом System Generator стандартные элементы игнорируются), стандартные библиотечные элементы Simulink используются в модели для симулирования внешних устройств. Для замены отсутствующих в библиотеке Xilinx элементов, реализующих необходимые для задачи моделирования функции, используются полностью конфигурируемые элементы Black Box, MCode, EDK Processor, имеющие различные возможности для реализации необходимых функций (Рис. 11).

Элементы Gateway In и Gateway Out необходимы для моделирования портов ввода/вывода ПЛИС, а также для связи со стандартными библиотечными элементами Simulink (симулирующими внешние устройства) (Рис. 12).

Элементы Gateway In и Gateway Out позволяют назначить конкретные выводы микросхемы ПЛИС для использования в качестве портов ввода/вывода в формате , (Рис. 13)

где MSB – номер вывода старшего бита, LSB – номер вывода младшего бита. То есть перечисляются номера контактов микросхемы ПЛИС, начиная со старшего бита в одинарных кавычках (контактные выводы называются по координатам их расположения, к примеру: ‘A11’, ‘D12’, что берется из Даташитины на конкретную ПЛИС) (Рис. 14).

Назначать контакты для выводов следует только в том случае, если их расположение критично для дальнейшей привязки в конкретном устройстве, а назначать выводы в среде Xilinx 11 лень:). Также преобразуют типы данных, используемых средой Simulink в тип данных, используемых в ПЛИС (с фиксированной точкой).

Также во всех библиотечных элементах Xilinx присутствует возможность жестко задать количество и вид используемых внутренних элементов ПЛИС (Рис. 15)

(элементы могут задаваться как в ручную, так и предварительно рассчитываться с помощью элемента Resource Estimator) (Рис. 16).

После создания симуляционной модели из библиотечных элементов необходимо сгенерировать проект для Xilinx 11.

2. Генерация проекта модели для Xilinx 11.

Для генерации проекта Xilinx с помощью System Generator производим настройки генерации проекта (Рис. 17).

а) Установить опции компилятора, директорию в которую будет производиться запись сгенерированного проекта Xilinx 11 (Target directory), язык в котором будет генерироваться проект (VHDL);

б) Установить тип используемой ПЛИС – Virtex5 xc5vlx50-3ff324 (поле – Part);

в) Установить параметры тактирующего сигнала: период одного такта 10 нс (FPGA clock period);

г) Установить период симуляции 1 (определяет количество шагов симуляции модели

за один цикл тактирующего сигнала).

По нажатию кнопки Generate происходит генерация проекта в указанную директорию, формируются: файл проекта (*.xise) файлы кодов на языке VHDL (*.vhd) и другие.

Для дальнейшей работы и конфигурирования файла прошивки ПЛИС необходимо открыть проект в программе Project Navigator (Рис. 18).

Выбрать пункт [Open Project] и в директории, указанной при генерации проекта открыть файл с расширением *.xise.

Экран программы разделен на области (Рис. 19):

Иерархия проекта (Hierarchy) (Рис. 20).

Позволяет смотреть состав и иерархию проекта, добавлять и удалять файлы проекта.

Настраивать свойства проекта, такие как тип используемой ПЛИС, тип корпуса используемой ПЛИС.

Область действий над проектом (Processes) – позволяет синтезировать проект, формировать отчеты по временным и другим характеристикам, формировать файл прошивки ПЛИС (Рис. 21).

Если ранее при построении модели не были заданы контактные выводы для портов ввода/вывода, то для продолжения работым над проектом и формирования файла прошивки необходимо назначить выводы ПЛИС для портов ввода/вывода. Для этого необходимо зайти в Раздел User Constraints (пользовательские установки) и выбрать пункт I/O Pin Planing (PlanAhead) – Pre-Syntesis (Рис. 22).

Откроется программа PlanAhead, входящая в программный пакет Xilinx 11 (Рис. 23).

В окне программы можно просмотреть порты ввода/вывода проекта, размещение контактных площадок корпуса, выбранной ПЛИС, структурное строение ПЛИС.

Чтобы сконфигурировать контактные выводы ПЛИС необходимо в области I/O Ports вызвать контекстное меню на All ports и выбрать пункт Auto-place I/O ports (Рис. 24) (если плата еще не разведена)

или в области просмотра контактных площадок для каждого вывода вручную назначить каждую ножку ПЛИСины (Рис. 25).

После определения выводов ПЛИС, необходимо сохранить изменения и закрыть программу PlanAhead.

В области действий над проектом, в окне программы Project Navigator, запускаем синтез проекта (Рис. 26).

Во время синтеза проекта, программа Xilinx производит рассчет и формирование логических цепей проекта.

После синтеза проекта, необходимо сгенерировать и строссировать внутренние соединения, для чего необходимо запустить на исполнение пункт Implement Design (Рис. 27).

После троссировки и построения внутренней структуры необходимо сформировать файл прошивки ПЛИС (Рис. 28).

По выполнении этой команды в папке проекта формируется файл прошивки ПЛИС (на самом деле в зависимости от типа ПЛИС это или файл прошивки для нее самой, или шаблон для формирования прошивки внешней загрузочной памяти) (по умолчанию фармируется двоичный файл *.bit)

3. Прошивка проекта в ПЛИС.

Для прошивки файла программы в ПЛИС (или во внешнюю загрузочную память) необходимо в области действий над проектом запустить пункт Configure Target Device, для создания прошивочного файла, конфигурации и осуществления загрузки в реальное устройство (Рис. 29).

После запуска iMPACT в области действий (iMPACT Flows) необходимо выполнить пункт Create PROM File, для формирования файла прошивки EEPROM для ПЛИС Virtex (Рис. 31) (которая с внешней памяти грузится).

При этом запустится мастер настройки формата файла прошивки ПЛИС.

На первом шаге необходимо выбрать необходимый носитель файла прошивки ПЛИС, в зависимости от типа ПЛИС (в данном случае Xilinx Flash/PROM, то есть микросхема памяти производства Xilinx).

На втором шаге необходимо выбрать размер микросхемы памяти (есть возможность автоматического выбора размера носителя на этапе создания файла прошивки) (Рис. 32, 33, 34).

Для добавления устройства необходимо выбрать ранее сформированный bit-файл. Устройство (конкретная микросхема) будет добавлена соответственно сформированному проекту (Рис. 36).

В связи с тем, что от одной микросхемы памяти может загружаться больше одной ПЛИС, существует возможность формирования единого прошивочного файла для одной микросхемы памяти (в случае достаточности объема памяти) (Рис. 37).

После добавления устройств, в области операций (iMPACT Processes) необходимо запустить пункт «Generate File», после завершения которого, будет выбрана конкретная микросхема памяти и сгенерирован соответствующий файл прошивки (Рис. 38, 39).

После формирования файла прошивки микросхемы памяти необходимо произвести подключение программатора (например Platform Cable USB) к ПК и устройству, содержащему программируемые микросхемы. Физическое подключение программатора следует производить при выключенном напряжении питания программируемого устройства (Рис. 40). После завершения всех соединений напряжение питания программируемого устройства необходимо включить.

После включения напряжения питания светодиод статуса на программаторе загорится зеленым светом, что сигнализирует о готовности программирования целевого устройства.

Для продолжения программирования в области действий необходимо запустить на исполнение пункт Boundary Scan (Рис. 41).

После запуска команды Boundary Scan в основной области программы по контекстному меню (правая кнопка мыши) необходимо выбрать пункт Initialize Chain (Рис. 42).

Программа подключится через программатор к программируемому устройству и определит микросхемы находящиеся на линии программирования (Рис. 43).

После определения микросхем находящихся в целевом устройстве необходимо назначит соответствующие по формату файлы для прошивки в конкретные микросхемы (Рис. 44, 45).

После назначения файлов необходимо настроить свойства программирования целевой микросхемы (в данном случае целевой микросхемой является только микросхема памяти). В окне свойств необходимо установить, назначение микросхемы (загрузка ПЛИС – Load FPGA), режим загрузки (параллельный – Parallel Mode), режим работы (Master/Slave) (Рис. 46).

После настройки свойств программирования в области операций необходимо запустить пункт Program (Рис. 47, 48, 49).

После окончания программирования нужно отключить напряжение питания от программируемого устройства и отключить от него программатор. И радоваться бесполезному устройству:)

В общем вкратце описал, позже расскажу как на ПЛИСинах в Симулинке делать более полезные устройства, цифровые фильтры к примеру, или ШИМ на стопиццот серв;)

Читайте также: